Mirza, M. M., MacLaren, D. A., Samarelli, A., Holmes, B. M., Zhou, H., Thoms, S., MacIntyre, D., and Paul, D. J. (2014) Determining the electronic performance limitations in top-down fabricated Si nanowires with mean widths down to 4 nm. Nano Letters, 14 (11). pp. 6056-6060. ISSN 1530-6984

Copyright © 2014 American Chemical Society

http://eprints.gla.ac.uk/99267

Deposited on: 21 November 2014

pubs.acs.org/NanoLett

# Determining the Electronic Performance Limitations in Top-Down-Fabricated Si Nanowires with Mean Widths Down to 4 nm

Muhammad M. Mirza,<sup>†</sup> Donald A. MacLaren,<sup>‡</sup> Antonio Samarelli,<sup>†</sup> Barry M. Holmes,<sup>†</sup> Haiping Zhou,<sup>†</sup> Stephen Thoms,<sup>†</sup> Douglas MacIntyre,<sup>†</sup> and Douglas J. Paul\*,<sup>†</sup>

<sup>†</sup>School of Engineering, University of Glasgow, Rankine Building, Oakfield Avenue, Glasgow G12 8LT, United Kingdom \*SUPA School of Physics and Astronomy, University of Glasgow, Kelvin Building, University Avenue, Glasgow G12 8QQ, United Kingdom

Supporting Information

ABSTRACT: Silicon nanowires have been patterned with mean widths down to 4 nm using top-down lithography and dry etching. Performancelimiting scattering processes have been measured directly which provide new insight into the electronic conduction mechanisms within the nanowires. Results demonstrate a transition from 3-dimensional (3D) to 2D and then 1D as the nanowire mean widths are reduced from 12 to 4 nm. The importance of high quality surface passivation is demonstrated by a lack of significant donor deactivation, resulting in neutral impurity scattering ultimately limiting the electronic performance. The results indicate the important parameters requiring optimization when fabricating nanowires with atomic dimensions.

KEYWORDS: Silicon nanowire, electronic transport, scattering mechanisms, 3D, 2D, 1D

Inderstanding the electronic transport properties of nanowires is essential to allow high performance devices to be optimized for a range of applications. Silicon nanowires have potential uses in a wide range of devices and applications which include transistors, <sup>1–3</sup> qubits, <sup>4,5</sup> photovoltaics, <sup>6</sup> thermoelectric generators, <sup>7</sup> biosensors, <sup>8,9</sup> and color selective photodetectors. <sup>10</sup> A number of studies have investigated effects which include donor deactivation, <sup>11</sup> surface roughness scattering, <sup>12</sup> and noise, 13 but being able to measure the carrier density directly rather than inferring the value from electrical conductivity values has been more of a challenge. While Hall effect measurements on single InP nanowires have recently been reported, 14 only carrier densities and mobilities have been extracted. Here we demonstrate direct measurements of the temperature dependence of the resistivity, carrier density, and mobility on a range of Si nanowires through the nanofabrication of small test structures that allow the length scales and the performance limiting scattering mechanisms to be determined.

Many of the electronic transport studies of Si nanowires described above have been on chemically grown nanowires using bottom-up technology; 1,8,9,11,13 however, industry still relies on top-down fabrication routes for manufacture to achieve high yields. In this paper, results are presented for topdown-fabricated nanowires with a range of mean widths from 45 down to ~4 nm. Both two-terminal and four-terminal structures including Hall bars and Greek crosses were fabricated to allow the resistivity, the carrier density, and the mobility to be extracted directly as a function of temperature. Such devices with features small enough to enable the extraction of the

carrier density has been enabled by the development of electron beam lithography and reactive ion etch processes enabling sub-10 nm features without the usual shrinking tricks required to deliver devices with these dimensions. 15 These test structures allowed the electronic properties to be studied as a function of temperature, enabling the major scattering processes dominating electronic transport to be identified directly rather than induced from, for example, the performance of transistors. 16 This is important because some dry etch processes can damage the surfaces of materials; hence, top-down fabricated nanowires could potentially be limited by different scattering mechanisms from bottom-up grown nanowires. In the present work, we determine the critical length scales and demonstrate that electronic transport for the degenerately doped silicon nanowires changes from 3D for the 12 nm mean width to predominantly 2D (7 nm mean width), and for the smallest nanowire with mean width of 4 nm, 1D transport is observed. We also extract for the first time the performance limiting scattering mechanism for Si nanowires at these dimensions.

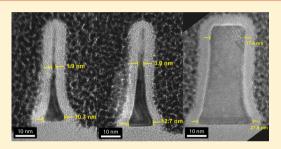

The fabrication of the Si nanowires is detailed in the Supporting Information. Large area Hall bar, four-terminal measurements were used to determine that the activated dopant density were nominally 2, 4, 8, and  $20\times10^{19}~\text{cm}^{-3}$  for samples produced from four different wafers. Figure 1 provides cross-sectional transmission electron microscopy (TEM)

Received: April 25, 2014 Revised: September 14, 2014 Published: October 9, 2014

6056

**Figure 1.** Cross-sectional TEM image of a Si nanowire fabricated by etching (a) with a 10 nm HSQ lithographically defined resist line after thermal oxidation and (b) with 30 nm HSQ lithography defined resist. The samples are surrounded by an amorphous Pt protection layer deposited by focus ion beam during the sample preparation for TEM.

images of 10 and 30 nm wide lithographically written nanowires. Clear footing from the etch and also an enhanced oxidation rate for the top corners of the nanowires are visible from the TEM characterization. The TEM images and capacitance-voltage measurements also confirm the SiO2 thickness to be ~4 nm. For the 10 nm written nanowire on the left of Figure 1, the top section of the Si is as small as 1.9 nm while the bottom foot is 10.7 nm. A similar effect is visible in the TEM micrographs of all the nanowire. The widths quoted for the rest of the paper are the mean values of ten cross-sectional measurements of the physical silicon widths over ten positions equally spaced in height throughout the nanowire. This then defines the width of the nanowire on the left of Figure 1 as 4 nm, but it should be clear that the majority of any electronic transport in the nanowire will be dominated by that in the wider 10.7 nm section at the bottom of the

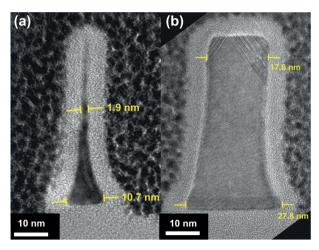

Details of the ac constant current electrical measurement techniques used to minimize electron heating are described in the Supporting Information. All presented data are from Hall bars (Figure 2). The Hall effect requires the measurement of the Hall voltage generated across the width of the nanowire and is independent of the cross-sectional geometry of the nanowires. The geometrical accuracy (including the error from nonuniformity) of the Hall measurement 17 is dependent on the width of the voltage probes compared to the width of the nanowire. For nanowires with widths below 20 nm, the proximity effect in electron beam lithography will increase the width of the nanowire and probe at the junction between the two (see Figure 2), reducing the accuracy of any extracted Hall voltage. An additional issue is the requirement to have wider current probes attached to the nanowire to minimize the access resistance to prevent any heating. A final issue for such heavily doped nanowires is that the actual Hall voltage is extremely small. For the Hall bars fabricated below 20 nm mean width, the geometrical uncertainty<sup>17</sup> in measuring the carrier density from the Hall effect only provides a value accurate to within a factor of 2 of the true value. Greek cross test structures (inset to Figure 2) were therefore designed to allow measurement of the carrier density by the Hall effect with geometrical uncertainty below 1% even for nanowires of 7 nm width. The smallest

**Figure 2.** SEM image of a 4 nm mean width Si nanowire with four terminal connections used to measure the mobility. Inset: a Greek cross with 12 nm probes used to measure the carrier density.

nanowire of mean width 4 nm will have a larger uncertainty and can only be estimated to be accurate to within a factor of 2 of the true value. The Hall voltage was extracted from a linear fit to data obtained by a -1 to +1 T magnetic sweep to remove any stray field effects. Both types of device demonstrated nominally identical carrier densities, and so the data from the Hall bars will be presented.

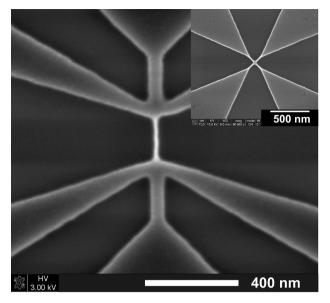

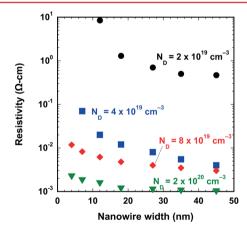

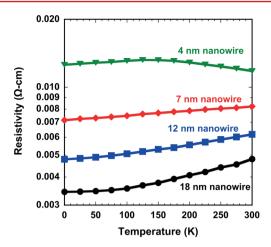

Figure 3 demonstrates the electrical resistivity measured from two terminals of the Hall bars fabricated with four different

**Figure 3.** Two-terminal resistivity measurements of nanowires with different widths for four different doping densities. For the lower doping densities, the smallest nanowires were fully depleted.

doping concentrations. For the lowest doping of  $2\times 10^{19}~\rm cm^{-3}$ , all nanowires with widths below 10 nm had resistivities greater than 100 M $\Omega$  while for the  $4\times 10^{19}~\rm cm^{-3}$  doped devices only the smallest nanowire had similar insulating properties, demonstrating the depletion of the complete nanowire for the lower doped samples. Only for the nanowires doped at  $8\times 10^{19}~\rm cm^{-3}$  or above could the electrical properties be extracted for widths down to  $\sim 4$  nm. Figure 4 demonstrates the four-terminal resistivity as a function of temperature. The larger nanowires all demonstrate strong metallic behavior which is to

**Figure 4.** Four-terminal resistivity measured for devices doped at  $8 \times 10^{19}$  cm<sup>-3</sup> as a function of temperature.

be expected since the doping is significantly above the Mott criterion  $^{18}$  for Si:P of  $3.5 \times 10^{18}$  cm $^{-3}$ . The nanowire with mean width of 4 nm demonstrates different behavior, suggesting that the depletion of the conducting part of this nanowire may have reduced the dimensionality for the electron transport to 1D.

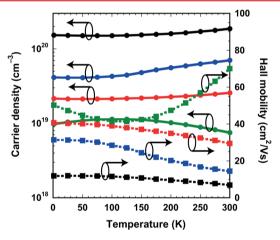

Figure 5 provides a plot of the carrier density and Hall mobilities extracted from four-terminal measurements on the

**Figure 5.** Mobility (squares) and carrier density (circles) as a function of temperature measured for Si nanowires with mean widths of 4 nm (green), 7 nm (red), 12 nm (blue), and 18 nm (black) all doped at  $8 \times 10^{19}$  cm<sup>-3</sup>.

Hall bars with nanowires mean widths of 4, 7, 12, and 18 nm (Figure 2) doped at  $\sim 8 \times 10^{19} \ \rm cm^{-3}$ . The extraction of 1.5  $\times$   $10^{20} \ \rm cm^{-3}$  for the widest nanowire demonstrates the difficulty in extracting accurate carrier density values at these dimensions, but the results for all nanowires do demonstrate the expected trends as the widths, doping, and temperature are varied. The mean width 7, 12, and 18 nm nanowires all demonstrate the

carrier density reducing as the temperature is reduced, suggesting activated behavior. The 4 nm mean width nanowire, however, has anomalous behavior probably due to larger geometrical uncertainty in extracting the carrier density, but it may also be related to a change to lower dimensions for the electronic transport. The doping for the 12 nm mean width nanowire was nominally  $8\times10^{19}~\rm cm^{-3}$  while the measured density at 300 K is  $7\times10^{19}~\rm cm^{-3}$  and the density reduces to 4.1  $\times$   $10^{19}~\rm cm^{-3}$  at 1.4 K. To extract drift mobilities from the Hall mobilities requires knowledge of the Hall factor. The Hall factor is dependent on the dominant scattering mechanism which will be determined below from temperature-dependent measurements. As the width of the nanowires is reduced, the carrier density is also reduced through surface depletion, resulting in a reduced carrier density.

The electrical width of the nanowire is unlikely to be the same as the physical width determined from the TEM measurements (Figure 1). For nondegenerate semiconductors, the depletion approximation allows the sidewall depletion width to be determined enabling the electrical width to be determined. For the degenerately doped Si nanowires in this study, the depletion approximation is not valid. Theoretical analysis of electron-electron and electron-impurity interactions 19 and the p-n junction potentials 20 in degenerately doped semiconductors indicate that the correct screening length is the Debye length which equals  $L_{\rm D} = (\varepsilon_0 \varepsilon_{\rm r} k_{\rm B} T /$  $(q^2N_D)^{1/2}$ , where  $\varepsilon_0$  is the permittivity of a vacuum,  $\varepsilon_r$  is the relative dielectric constant,  $k_{\rm B}$  is Boltzmann's constant, T is the temperature, q is the electronic charge, and  $N_D$  is the activated donor density. A simple approach for the present tall nanowires is therefore to define the electrical width as the physical width minus twice the Debye screening length. Table 1 provides a summary of the maximum and minimum conducting electrical widths of the nanowires and the height over which electrical conduction occurs after removing  $L_{\rm D}$  from the side of each nanowire. The values of  $L_{\rm D}$ , the 3D Fermi wavelength  $\lambda_{\rm F}$ , and the mean free path  $l_{\rm 3D}$  are presented in Table 1 where  $\lambda_{\rm F}=2\pi(g_{\rm v}/3\pi^2n)^{2/3}$  ( $g_{\rm v}$  is the valley degeneracy = 2 for the Si conduction band and n the carrier density). The mean free paths are  $l_{\rm 3D} = (\hbar \mu/q) (3\pi^2 (n_{\rm 3D}/q_{\rm v}))^{1/3}$  and  $l_{\rm 2D} = (\hbar \mu/q) (2\pi (n_{\rm 2D}/g_{\rm v}))^{1/2}$ . It is clear that the 12 and 18 nm mean width nanowires are 3D while the 7 nm nanowire is predominantly 2D, but the bottom foot section will have some 3D transport. The smallest 4 nm mean width nanowire is at least 2D, but due to the shape in Figure 1, the electrical dimensions in Table 1, and the value of *l*, the transport will be 1D. These results demonstrate that for such heavily doped nanowires the transport is only 1D for the smallest nanowire dimensions.

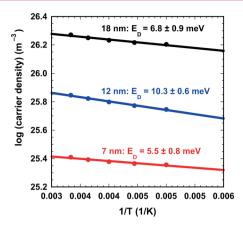

The activated part of the slope of the carrier density versus temperature was used to extract the donor activation energy for the 7, 12, and 18 nm wide nanowires using four-terminal Hall measurements. Figure 6 presents a log—log plot of the data fitted to the activated function for the carrier density,  $n \propto$

Table 1. Main Length Scales at 300 K for Four Nanowires Doped at  $\sim$ 8 × 10<sup>19</sup> cm<sup>-3</sup>

| mean nanowire width (nm) | max electrical width (nm) | min electrical width (nm) | electrical height (nm) | $L_{\mathrm{D}}$ (nm) | $\lambda_F$ 3D (nm) | l (nm) | dimension |

|--------------------------|---------------------------|---------------------------|------------------------|-----------------------|---------------------|--------|-----------|

| 4                        | 9.2                       | 0.1                       | 18.1                   | 1.5                   | 13                  | 20.4   | 1D        |

| 7                        | 11.1                      | 1.4                       | 42.3                   | 0.81                  | 8.7                 | 6.7    | 2D/3D     |

| 12                       | 18.5                      | 6.0                       | 51.0                   | 0.49                  | 6.2                 | 6.2    | 3D        |

| 18                       | 25.6                      | 12.4                      | 51.9                   | 0.30                  | 4.5                 | 4.5    | 3D        |

**Figure 6.** Extraction of the dopant activation energy from 7, 12, and 18 nm wide Si nanowires doped at  $8 \times 10^{19}$  cm<sup>-3</sup>.

$\exp(E_{\rm D}/2k_{\rm B}T)$ , where  $E_{\rm D}$  is the donor activation energy. Importantly, the activation energies extracted for the nanowires with mean widths of 7, 12, and 18 nm are all significantly lower than those demonstrated from similar bottom-up grown nanowires without passivation. The lower  $E_D$  for the 7 nm wide nanowire compared to the larger nanowires is a result of the change from 3D to 2D screening. The 4 nm nanowire did not demonstrate activated behavior probably due to the high geometrical uncertainty in extracting the carrier density, but this may also be related to a change in transport dimension. Donor deactivation was demonstrated to be the main issue for the unpassivated bottom-up grown nanowires. 11 The 12 nm mean width nanowire results in Figure 5 demonstrate far lower activation energies of  $10.3 \pm 0.6$  meV compared to the 46 meV of a grown 15 nm wide nanowire. 11 This is due to the thermal oxide passivation used in the present work with a dielectric constant of 3.9 around the nanowire compared to air of 1, which significantly reduces the donor deactivation effect.<sup>21</sup> Large capacitors used to characterize the thermal oxide indicate a low surface trapped charge density of  $5 \times 10^{10}$  cm<sup>-2</sup> eV<sup>-1</sup>. which will also improve the electronic properties. The different etched facets on the nanowires will result in higher surface state densities than capacitors fabricated on the (001) surface of Si, but the densities will be significantly lower than any surfaces without a thermal oxide. Our results demonstrate the importance of a high quality passivation layer on nanowires with widths below ~30 nm to prevent reductions in the carrier densities especially at low temperatures and to provide high performance for the electronic properties.

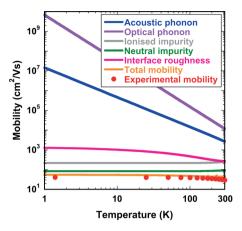

The scattering mechanism which limits the mobility in the present nanowires was determined by studying the temperature dependence of the experimental Hall mobility and comparing it to a number of theoretically calculated mobilities for specific scattering mechanisms. Figure 7 plots the experimental Hall mobilities versus the drift mobility calculated for acoustic phonon scattering, 22 longitudinal-optical (LO) nonpolar optical phonon scattering, 22,23 degenerate ionized impurity scattering, 22,24 neutral impurity scattering, and interface roughness scattering (see Supporting Information for details). The total mobility was estimated using Matthieson's rule. While the Matthieson's rule approach has significant uncertainty as the weighting of the scattering mechanisms is not taken into account, it has sufficient accuracy to allow the dominant scattering mechanism to be determined without the requirement of detailed Monte Carlo modeling approaches.

Figure 7. Experimental Hall mobility compared to the drift mobility for different scattering processes for the 7 nm Si nanowire doped at  $8 \times 10^{19} \text{ cm}^{-3}$ .

The dominant mobility limiting scattering mechanism was found to be neutral impurity scattering (Figure 7). Ridley has previously stated the importance of this mechanism for heavily doped semiconductors,<sup>24</sup> and the mobility was modeled using<sup>25</sup>

$$\mu_{\rm NI} = \frac{m^* q^3}{20\varepsilon_0 \varepsilon_{\rm r} (N_{\rm D} - n)\hbar^3} \tag{1}$$

where n is the measured carrier density,  $N_{\rm D}$  is the donor density, and  $\hbar$  is Planck's constant divided by  $2\pi$ . For all the modeling, the effective mass with nonparabolicity parameter<sup>27</sup>  $C=0.5~{\rm eV}^{-1}$  was used since the Fermi level will be inside the conduction band and is given by  $m^*=m_{\rm c}^*[1+2C(\hbar^2/m_{\rm c}^*)(3\pi^2n/g_{\rm v})^{2/3}]$ , where  $m_{\rm c}^*$  is the conductivity effective mass  $(=3(1/m_{\rm l}+2/m_{\rm t})^{-1})$  with  $m_{\rm l}=0.98m_{\rm 0}$  and  $m_{\rm t}=0.198m_{\rm 0}$  with  $m_{\rm 0}$  the free electron mass.

The interface roughness scattering model was a Gaussiantype autocorrelation for an interface roughness height of  $\Delta$  and lateral correlation length of  $\Lambda$  as detailed by Motohisa and Sakaki.<sup>26</sup> A Gaussian model was chosen as it has demonstrated better fits to the experimental mobility in quantum well devices without a vertical electrical field while the exponential model used in MOSFETs has demonstrated superior descriptions of the mobility under large vertical electrical fields.<sup>28</sup> For the present nanowires, line edge roughness from the electron beam lithography is expected to be the largest factor in determining the roughness values. The electrical width for the nanowire with mean width of 7 nm was taken to be the physical width minus twice the Debye length since the device is 2D for electrical transport (Table 1). The interface roughness scattering was not found to be significant compared to the neutral impurity scattering, and even with large roughness values of  $\Delta$  = 2 nm and  $\Lambda$  = 1 nm (cf. silicon MOSFET  $\Delta$  = 0.43 nm and  $\Lambda = 0.15 \text{ nm}^{29}$ ) the interface roughness scattering was still insignificant compared to the other scattering mechanisms. Previous measurements of the Q of Si photonic microrings<sup>30</sup> to extract the roughness parameters has suggested the line edge roughness using the same electron beam lithography and dry etch tools is  $\Delta = 0.5$  nm, further indicating that interface roughness scattering is unlikely to be significant.

As neutral impurity scattering is dominating the transport (Figure 7) the Hall scattering parameter is therefore 1, and so for these degenerately doped nanowires the drift mobility is equal to the Hall mobility.<sup>22</sup> While the Hall factor for many

degenerate semiconductors<sup>22</sup> is normally set to 1, our results are important confirmation that the dominant scattering mechanisms extracted from the temperature-dependent mobility measurements confirm this value experimentally.

A number of papers have demonstrated that for sufficiently small widths of Si nanowires with (001) orientations and appropriate surface passivation that the band gap can increase and the band structure can change from indirect to direct.<sup>31</sup> In the present case the nanowires are too wide for such significant band structure modifications, and the band structure is expected to be close to the bulk Si band structure. The present Si nanowires with mean widths of <7 nm. however, are sufficiently small for changes to the phonon dispersion.<sup>32</sup> At low temperatures experimental Raman studies have even demonstrated phonon confinement effects in Si nanowires with diameters up to 25 nm at room temperature.<sup>33</sup> All the nanowires in this work have comparable doping and dimensions to those which have demonstrated up to 150 reduction in the thermal conductivity at room temperature, enhanced Seebeck coefficients, and improved thermoelectric performance, indicating enhancements to the density of states and phonon transport from the reduction in dimensionality. While phonon dispersions will have effects for the present nanowire dimensions, theoretical modeling has indicated that interface roughness scattering is predicted to be the dominant mechanism reducing the thermal conductivity at these dimensions<sup>32,34</sup> rather than the phonon confinement effects.

In conclusion, the transport properties of degenerately doped Si nanowires with mean widths down to 4 nm have been determined through temperature-dependent measurements to be limited by neutral impurity scattering. Nanowires with mean widths above 12 nm are 3D while 7 nm nanowires have a transition to 2D behavior. The extracted length scales for the smallest nanowires of mean width 4 nm indicate it has 1D electronic transport. The Hall factor was determined from experiments to be 1, indicating that the Hall and drift mobilities are equal for these top-down-fabricated nanowires. Donor deactivation and surface roughness which have been demonstrated to dominate a number of bottom-up-fabricated nanowires were not determined to be significant for these top-down-fabricated nanowires, indicating the importance of high quality surface passivation for all nanowires at these length scales.

### ASSOCIATED CONTENT

# S Supporting Information

Fabrication methods, electrical characterization, and the formulas and parameters used to calculate all the scattering mechanisms in Figure 7. This material is available free of charge via the Internet at http://pubs.acs.org.

### AUTHOR INFORMATION

## **Corresponding Author**

\*E-mail: Douglas.Paul@glasgow.ac.uk (D.J.P.).

# Notes

The authors declare no competing financial interest.

# ACKNOWLEDGMENTS

The work was funded by the U.K. EPSRC from grant EP/H023107/1. The authors thank the staff of the James Watt Nanofabrication Centre for help and support in undertaking the research.

## REFERENCES

- (1) Appenzeller, J.; Knoch, J.; Bjork, M.; Riel, H.; Schmid, H.; Riess, W. IEEE Trans. Electron Devices 2008, 55, 2827–2845.

- (2) Colinge, J.-P.; Lee, C.-W.; Afzalian, A.; Akhavan, N. D.; Yan, R.; Ferain, I.; Razavi, P.; O'Neill, B.; Blake, A.; White, M.; Kelleher, A.-M.; McCarthy, B.; Murphy, R. *Nat. Nanotechnol.* **2010**, *5*, 225–229.

- (3) Hu, Y.; Xiang, J.; Liang, G.; Yan, H.; Lieber, C. M. Nano Lett. 2008, 8, 925-930.

- (4) Nadj-Perge, S.; Frolov, S. M.; Bakkers, E. P. A. M.; Kouwenhoven, L. P. *Nature* **2010**, 468, 1084–1087.

- (5) Hu, Y.; Kuemmeth, F.; Lieber, C. M.; Marcus, C. M. Nat. Nanotechnol. 2012, 7, 47–50.

- (6) Tian, B.; Zheng, X.; Kempa, T. J.; Fang, Y.; Yu, N.; Yu, G.; Huang, J.; Lieber, C. M. *Nature* **200**7, 449, 885–889.

- (7) Boukai, A. I.; Bunimovich, Y.; Tahir-Kheli, J.; Yu, J. K.; Goddard, W. A.; Heath, J. R. *Nature* **2008**, *451*, 168–171.

- (8) Zheng, G.; Patolsky, F.; Cui, Y.; Wang, W. U.; Lieber, C. M. Nat. Biotechnol. 2005, 23, 1294–1301.

- (9) Zheng, G.; Gao, X. P. A.; Lieber, C. M. Nano Lett. 2010, 10, 3179-3183.

- (10) Park, H.; Dan, Y.; Seo, K.; Yu, Y. J.; Duane, P. K.; Wober, M.; Crozier, K. B. *Nano Lett.* **2014**, *14*, 1804–1809.

- (11) Bjork, M. T.; Schmid, H.; Knoch, J.; Riel, H.; Riess, W. Nat. Nanotechnol. 2009, 4, 103-107.

- (12) Wang, J.; Polizzi, E.; Ghosh, A.; Datta, S.; Lundstrom, M. Appl. Phys. Lett. 2005, 87, 043101.

- (13) Clément, N.; Han, X. L.; Larrieu, G. Appl. Phys. Lett. 2013, 103, 263504.

- (14) Storm, K.; Halvardsson, F.; Heurlin, M.; Lindgren, D.; Gustafsson, A.; Wu, P. M.; Monemar, B.; Samuelson, L. *Nat. Nanotechnol.* **2012**, *7*, 718–722.

- (15) Mirza, M. M.; Zhou, H. P.; Velha, P.; Li, X.; Docherty, K. E.; Samarelli, A.; Ternent, G.; Paul, D. J. J. Vac. Sci. Technol., B 2012, 30, 06FF02-1-8

- (16) Trivedi, K.; Yuk, H.; Floresca, H. C.; Kim, M. J.; Hu, W. Nano Lett. 2011, 11, 1412–1417.

- (17) Haeusler, J.; Lippmann, H. J. Solid-State Electron. 1968, 11, 173-182.

- (18) Edwards, P. P.; Sienko, M. J. Phys. Rev. B 1978, 17, 2575-2581.

- (19) Wolff, P. A. Phys. Rev. 1962, 126, 405-412.

- (20) Bernard, W.; Roth, H.; Schmid, A. P.; Zeldes, P. Phys. Rev. 1963, 131, 627–631.

- (21) Diarra, M.; Niquet, Y.-M.; Delerue, C.; Allan, G. Phys. Rev. B 2007, 75, 045301.

- (22) Morkoç, H. Nitride Semiconductor Devices: Fundamentals and Applications; Wiley-VCH: Weinheim, 2013.

- (23) Hamaguchi, C. Basic Semiconductor Physics; Springer: Berlin, 2001

- (24) Ridley, B. K. Quantum Processes in Semiconductors, 2nd ed.; Oxford University Press: New York, 1988.

- (25) Erginsoy, C. Phys. Rev. 1950, 79, 1013-1014.

- (26) Motohisa, J.; Sakaki, H. Appl. Phys. Lett. 1992, 60, 1315-1317.

- (27) Jacoboni, C.; Reggiani, L. Rev. Mod. Phys. 1983, 55, 645-705.

- (28) Goodnick, S. M.; Ferry, D. K.; Wilmsen, C. W.; Liliental, Z.; Fathy, D.; Krivanek, O. L. *Phys. Rev. B* **1985**, 32, 8171–8186.

- (29) Ando, T.; Fowler, A. B.; Stern, F. Rev. Mod. Phys. 1982, 54, 437-672.

- (30) Canciamilla, A.; Torregiani, M.; Ferrari, C.; Morichetti, F.; Rue, R. M. D. L.; Samarelli, A.; Sorel, M.; Melloni, A. *J. Opt.* **2010**, *12*, 104008.

- (31) Vo, T.; Williamson, A. J.; Galli, G. Phys. Rev. B 2006, 74, 045116.

- (32) Ramayya, E. B.; Maurer, L. N.; Davoody, A. H.; Knezevic, I. *Phys. Rev. B* **2012**, *86*, 115328.

- (33) Adu, K. W.; Gutiérrez, H. R.; Kim, U. J.; Sumanasekera, G. U.; Eklund, P. C. *Nano Lett.* **2005**, *5*, 409–414.

- (34) He, Y.; Galli, G. Phys. Rev. Lett. 2012, 108, 215901.