Bentley, S. et al. (2011) Electron mobility in surface- and buried- channel flatband  $In_{0.53}Ga_{0.47}As\ MOSFETs\ with\ ALD\ Al_2O_3\ gate\ dielectric$ . IEEE Electron Device Letters, 32 (4). pp. 494-496. ISSN 0741-3106

http://eprints.gla.ac.uk/52717/

Deposited on: 10 June 2011

> EDL-2010-12-2162 < 1

# Electron Mobility in Surface and Buried Channel Flatband In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs with ALD Al<sub>2</sub>O<sub>3</sub> Gate Dielectric.

Steven J. Bentley, *Member, IEEE*, Martin Holland, Xu Li, Gary W. Paterson, Haiping Zhou, Olesya Ignatova, Douglas Macintyre, Stephen Thoms, Asen Asenov, *Senior Member, IEEE*, Byungha Shin, Jaesoo Ahn, Paul C. McIntyre and Iain G. Thayne

Abstract—In this paper, we investigate the scaling potential of flatband III-V MOSFETs by comparing the mobility of surface and buried  $In_{0.53}Ga_{0.47}As$  channel devices employing an Atomic Layer Deposited (ALD)  $Al_2O_3$  gate dielectric and a delta-doped InGaAs/InAlAs/InP heterostructure.

Peak electron mobilities of 4300 cm<sup>2</sup>/V·s and 6600 cm<sup>2</sup>/V·s at a carrier density of 3×10<sup>12</sup> cm<sup>-2</sup> for the surface and buried channel structures respectively were determined. In contrast to similarly scaled inversion-channel devices, we find that mobility in surface channel flatband structures does not drop rapidly with electron density, but rather high mobility is maintained up to carrier concentrations around 4x10<sup>12</sup> cm<sup>-2</sup> before slowly dropping to around 2000 cm<sup>2</sup>/V·s at 1x10<sup>13</sup> cm<sup>-2</sup>. We believe these to be world leading metrics for this material system and an important development in informing the III-V MOSFET device architecture selection process for future low power, highly scaled CMOS.

Index Terms—InGaAs, MOSFET, ALD, electron mobility

# I. INTRODUCTION

HE continual requirements of the CMOS International Technology Roadmap for Semiconductors [1] for increased performance and density have led to the introduction of myriad non-classical performance boosters such as high-κ metal gate stacks and strained channels, and it is expected that continued EOT scaling will require the SiO<sub>2</sub> interfacial layer to be eliminated [2]. As a consequence, the III-V/high-κ interface has attracted significant interest, initially due to the potential of III-V structures for high electron velocity, evidenced by the high performance achieved in scaled III-V HEMTs [3]. It is now anticipated that III-V MOSFETs may allow higher drive

Manuscript received December 24, 2010. This work was supported in part by the UK Engineering and Physical Sciences Research Council under Grant EP/F002610/1 and the Semiconductor Research Corporation via the Nonclassical CMOS Research Center.

S. Bentley, M. Holland, X. Li, G. Paterson, H. Zhou, O. Ignatova, D. Macintyre, S. Thoms, A. Asenov and I.G. Thayne are with the Nanoelectronics Research Centre, School of Engineering, University of Glasgow, Glasgow, UK (e-mail: steven.bentley@glasgow.ac.uk).

B. Shin was with the Department of Materials Science and Engineering, Stanford University, Stanford, CA 94305 USA. He is now at IBM T.J. Watson Research Center, Yorktown Heights, NY 10598 USA.

J. Ahn and P.C. McIntyre are with the Department of Materials Science and Engineering, Stanford University, Stanford, CA 94305 USA (e-mail: pcm1@stanford.edu).

current and transconductance than silicon at its low power scaling limit [4], making them an attractive n-channel solution.

Much recent work [5-8] has focused on the development of inversion-mode III-V nMOSFETs. Such devices, though eminently silicon-like, have not demonstrated the superior transport potential of a heterostructure quantum well, enabled by the epitaxial techniques used in III-V fabrication. Conversely, much work has also been undertaken on the development of buried-channel quantum well nMOSFETs, but their scaling potential remains unclear as a consequence of the inclusion of wide-bandgap layers above the channel [4, 6].

In this letter, we present highly-scaled surface and buried channel flatband nMOSFET structures which maintain mobilities up to 4300 and 6600 cm<sup>2</sup>/V·s respectively, at electron densities relevant for device operation.

## II. EXPERIMENT

For the buried channel devices, the following layers were grown sequentially by molecular beam epitaxy on 2" semiinsulating (100) InP substrates: a 400 nm In<sub>0.52</sub>Al<sub>0.48</sub>As buffer, silicon δ-doping with a density of 3×10<sup>12</sup> cm<sup>-2</sup>, a 4 nm In<sub>0.52</sub>Al<sub>0.48</sub>As spacer, a 10 nm lattice-matched In<sub>0.53</sub>Ga<sub>0.47</sub>As channel, a 2 nm In<sub>0.52</sub>Al<sub>0.48</sub>As barrier and a 2 nm In<sub>0.53</sub>Ga<sub>0.47</sub>As cap. In the case of the surface channel structure, the upper two layers were omitted. Apart from the  $\delta$ -doping planes, all layers were nominally undoped. The wafers were then capped in situ in the MBE tool using an amorphous arsenic cap to protect the surface from oxidation, loaded into an ALD chamber and the arsenic cap desorbed in situ [10]. 60 cycles of Al<sub>2</sub>O<sub>3</sub> (approximately 6 nm) were then grown at 270°C using TMA and H<sub>2</sub>O precursors in a TMA-first ALD process [11]. MOSFETs were fabricated in two lithographic steps using a wrap-around gate, obviating the need for device isolation [12]. First, a platinum/gold gate was defined by electron beam lithography (EBL) and liftoff. Non-self-aligned ohmic contacts were then defined by EBL, selective wet etching of the Al<sub>2</sub>O<sub>3</sub> in dilute KOH and electron beam evaporation of Ni/Ge/Au-based ohmic contacts. The contacts were alloyed in a 60s RTA process in a nitrogen atmosphere at 280°C. MOS capacitors were simultaneously defined adjacent to the MOSFETs. The wafers underwent no additional post> EDL-2010-12-2162 < 2

deposition forming gas processing, which has been shown to reduce the interface state density (D<sub>it</sub>) [13].

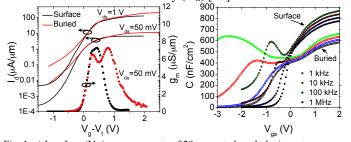

Fig. 1 a) Log  $I_{d,g_m}(V_{gs})$  measurements of 20  $\mu$ m gate length devices at  $V_d$ =50 mV and 1 V and matched gate overdrive. b) C-V measurements of 100  $\mu$ m diameter dots used for mobility extraction.

## III. RESULTS AND DISCUSSION

Typical log I<sub>d</sub>,g<sub>m</sub>(V<sub>gs</sub>) characteristics of surface and buried channel 20  $\mu$ m gate length devices at  $V_d = 50$  mV and 1 V are shown in Fig. 1. The surface and buried channel devices feature threshold voltages of -0.13 V and -0.87 V respectively. For comparison, transfer characteristics are shown for matched gate overdrive. At 2 V gate overdrive and  $V_d = 1 V$ ,  $I_d$  was 130  $\mu A/\mu m$  and 195  $\mu A/\mu m$  for the surface and buried channel devices respectively. At  $V_d = 50 \text{ mV}$ , the subthreshold swings of the surface and buried channel devices were 195 mV/dec and 430 mV/dec respectively. Calculating CET at threshold, these equate to approximate Dit figures of  $7.3\times10^{12}$  cm<sup>-2</sup> and  $1.8\times10^{13}$  cm<sup>-2</sup> respectively. We believe this difference may be due to the specific bandgap energies and therefore trap distributions swept by the Fermi level at the oxide/semiconductor interface in the two device structures as the gate voltage is varied. Another notable feature in Fig. 1a is the "double-peak" in the g<sub>m</sub>(V<sub>g</sub>) characteristic of the buried channel device, which we believe reflects charge transfer from the channel to the upper semiconductor layers at higher gate bias. Multi-frequency C-V measurements of 100 µm diameter MOS capacitors are also included in Fig. 1. The measured maximum capacitance scales with CET as expected when considering the additional semiconductor layers in the buried structure.

The surface channel devices featured on-resistances of  $3030~\Omega \cdot \mu m$  and total access resistance of  $1140~\Omega \cdot \mu m$  per side. As a consequence of lower sheet resistance, the buried channel devices had figures of  $1160~\Omega \cdot \mu m$  and  $540~\Omega \cdot \mu m$  respectively.

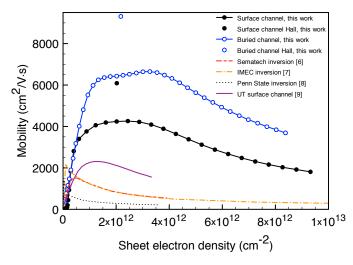

Effective mobility was extracted as a function of the channel electron concentration using a combination of I-V and C-V measurements. The wrap-around gate process precludes conventional split-CV characterization, hence the mobility is determined by extracting the gate voltage dependent channel carrier density from C-V<sub>g</sub> capacitor measurements at 1 MHz and low-field  $I_{ds}$ -V<sub>gs</sub> from an adjacent MOSFET at  $V_d = 50 \, \text{mV}$  [12]. The resultant room temperature mobility/carrier concentration data are shown in Fig. 2. Many data, e.g. [5], published for III-V inversion channel mobility include a "correction" for the effect of the interface state density, using simulated capacitance data. It should be noted that we employ no such correction. Also shown for comparison are mobility data from various inversion channel

In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs [6-8] and Hall data extracted from Van der Pauw structures for both flatband designs.

Fig. 2 Mobility of surface and buried channel flatband devices as compared to various ALD/In<sub>0.53</sub>Ga<sub>0.47</sub>As inversion mode devices (dashed) from [6-8] and a fully-undoped surface channel quantum well [9]. In contrast to other devices, surface channel flatband devices exhibit high mobility over the complete electron density range, similar to buried channel devices.

The surface channel flatband design exhibits peak mobility of around 4300 cm<sup>2</sup>/V·s: significantly lower than the peak mobility of 6600 cm<sup>2</sup>/V·s extracted from the buried channel wafer, which may indicate increased roughness at the ALD oxide/channel interface over that of the epitaxial barrier/channel interface in buried channel devices. Extracted Hall mobilities on both structures are notably higher than those from transistor measurements, which may a result of the different extraction techniques, and particularly contribution of oxide charge to the capacitance. In both cases, however, the carrier concentration dependence of the mobility is notably different from the characteristics of inversion channel In<sub>0.53</sub>Ga<sub>0.47</sub>As devices, for which the mobility peaks at low electron concentration, then rapidly decreases with increasing density [6-8]. The mobility from our surface channel devices, in contrast, peaks at around 4300 cm<sup>2</sup>/V·s before decreasing with increasing electron density to around 2000 cm<sup>2</sup>/V·s at a density of 1×10<sup>13</sup> cm<sup>-2</sup>: behavior very similar to our buried channel devices. The only mobility data for surface channel quantum well devices in literature [9] are also included. Although otherwise similar, these devices do not feature delta doping, and their mobility, whilst higher than in an inversion channel, is relatively low and decays rapidly with increasing electron density in comparison to the data reported in this letter. The superior mobility of our devices may be explained by the use of both an undoped channel and quantum confinement in the presence of delta doping on the backside of the channel.

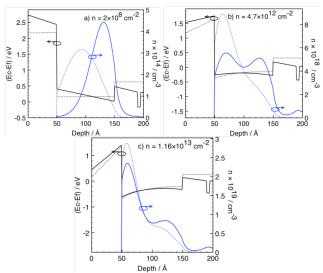

To explain the high mobility, numerical simulations of the electron populations of our surface channel flatband structure and a theoretical inversion mode device were undertaken, and are found in Fig. 3. Both configurations employ a lattice-matched 10 nm  $In_{0.53}Ga_{0.47}As$  channel on an  $In_{0.52}Al_{0.48}As$

> EDL-2010-12-2162 < 3

spacer to provide heterostructure confinement. In the inversion-channel device, the channel is p-doped at  $1 \times 10^{17}$  cm<sup>-3</sup>. The electron distributions in these two devices are compared for matched electron density in each case.

The mobility of the flatband device below threshold is likely limited by remote impurity scattering from the doping. Above threshold (Fig. 3a), the channel forms towards the back of the quantum well as a consequence of the delta doping, and a high electron density accumulates here initially, screening the dopant. In this region, the mobility is therefore largely unaffected by the oxide interface roughness scattering and dominated rather by that at the heterostructure interface.

As the gate bias is increased, electrons populate the whole channel (Fig. 3b), becoming subject to roughness scattering from both interfaces. Even at high bias (Fig. 3c), however, a significant fraction of the electrons remain at the rear of the channel, where mobility is at its maximum.

In contrast, as the inversion mode device switches on, the channel is formed close to the oxide interface. The p-doped depletion layer exerts a large vertical electric field on the inversion layer charge, which encounters strong oxide interface roughness scattering. The vertical electric field continuously increases with the increase of the channel carrier concentration as gate bias is increased. Consequently, the electron population is always subject to increased interface roughness scattering at the immediate oxide interface as compared to the flatband device.

Fig. 3 1-dimensional Poisson-Schrödinger simulations of electron populations of a surface channel flatband device (solid line) and an inversion mode device comprising a 10 nm  $In_{0.53}Ga_{0.47}As$  channel (dashed line), compared for matched electron densities. In each case, the flatband device electron density is less constrained to the oxide interface than in the inversion-mode device.

We believe that remote interface roughness and coulomb scattering from the oxide interface limit the mobility in our surface channel structure. In the buried channel, decreased proximity of the charge to the oxide interface further increases mobility. As a result, the vertical field dependence of the interface roughness scattering from the rear spacer interface becomes clearly identifiable at densities of  $1-4\times10^{12}$  cm<sup>-2</sup>.

### IV. CONCLUSION

The development of the surface channel flatband architecture has enabled the fabrication of well-behaved MOSFETs with mobilities of up to 4300 cm<sup>2</sup>/V·s which are sustained at high values up to channel carrier densities of 1x10<sup>13</sup> cm<sup>-2</sup>; similar to the characteristics of buried channel devices. This behavior, in contrast to inversion channel devices, arises as a direct consequence of the carrier and vertical electric field distributions in the flatband architecture, and indicates the potential of this materials architecture solution for future low power, highly scaled n-channel CMOS.

### REFERENCES

- [1] International Technology Roadmap for Semiconductors, 2009. [Online]. Available: http://www.itrs.net/Links/2009ITRS/Home2009.htm

- [2] H. Wong, D. Frank and P. Solomon, "Device design considerations for double-gate, ground-plane, and single-gated ultra-thin SOI MOSFET's at the 25 nm channel length generation.", *IEDM Tech. Dig.*, pp. 407-410, 1998.

- [3] D.-H. Kim and J. del Alamo, "30-nm InAs PHEMTs With  $f_T$  = 644 GHz and  $f_{max}$  = 681 GHz.", *IEEE Electron Device Lett.*, vol. 31, no. 8 pp. 806 808, 2010.

- [4] M. Radosavljevic, B. Chu-Kung, S. Corcoran, G. Dewey, M. K. Hudait, J. M. Fastenau, J. Kavalieros, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, W. Rachmady, U. Shah, and Robert Chau, "Advanced high-κ gate dielectric for high-performance short-channel In<sub>0.7</sub>Ga<sub>0.3</sub>As quantum well field effect transistors on silicon substrate for low power logic applications.", *IEDM Tech. Dig.*, pp. 319-322, 2009.

- [5] Y. Q. Wu, M. Xu, R.S. Wang, O. Koybasi and P. D. Ye, "High Performance Deep-Submicron Inversion-Mode InGaAs MOSFETs with maximum G<sub>m</sub> exceeding 1.1 mS/μm: New HBr pretreatment and channel engineering.", *IEDM Tech. Dig.*, pp. 323-326, 2009.

- [6] J. Huang, N. Goel, H. Zhao, C. Y. Kang, K.S. Min, G. Bersuker, S. Oktyabrsky, C.K. Gaspe, M.B. Santos, P. Majhi, P. D. Kirsch, H.-H. Tseng, J.C. Lee, and R. Jammy, "InGaAs MOSFET performance and reliability improvement by simultaneous reduction of oxide and interface charge in ALD (La)AlOx/ZrO<sub>2</sub> gate stack.", *IEDM Tech. Dig.*, pp. 335-338, 2009.

- [7] D. Lin, N. Waldron, G. Brammertz, K. Martens, W.-E Wang, S. Sioncke, A. Delabie, H. Bender, T. Conard, W. H. Tseng, J. C. Lin, K. Temst, A, Vantomme, J. Mitard, M. Caymax, M. Meuris, M. Heyns, T. Hoffmann, "Exploring the ALD Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As and Al<sub>2</sub>O<sub>3</sub>/Ge Interface Properties: A Common Gate Stack Approach for Advanced III-V/Ge CMOS." ECS Transactions, vol. 28, no. 5 pp. 173-183, 2010.

- [8] A. Ali, H. Madan, S. Koveshnikov and S. Datta, "Small-signal response of inversion layers in high-mobility In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFETs made with thin high-κ dielectrics." *IEEE Trans. Electron Devices*, vol. 57 pp. 742-748, 2010

- [9] H. Zhao, Y.-T. Chen, J. Hwan Yum, Y. Wang, N. Goel and J.C. Lee. "High performance In<sub>0.7</sub>Ga<sub>0.3</sub>As metal-oxide-semiconductor transistors with mobility >4400 cm<sup>2</sup>/Vs using InP barrier layer." *Appl. Phys. Lett.* vol. 94, no. 19 p. 193502, 2009.

- [10] E.J. Kim, E. Chagarov, J. Cagnon, Y. Yuan, A.C. Kummel, P.M. Asbeck, S. Stemmer, K.C. Saraswat and P.C. McIntyre, "Atomically abrupt and unpinned Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As interfaces: Experiment and simulation.", *J Appl Phys*, vol. 106, no. 12, p. 124508, 2009.

- [11] B. Shin, J.B. Clemens, M.A. Kelly, A.C. Kummel, and P.C. McIntyre, "Arsenic Decapping and Half-Cycle Reactions during Atomic Layer Deposition of Al<sub>2</sub>O<sub>3</sub> on In<sub>0.53</sub>Ga<sub>0.47</sub>As (001)," *Appl. Phys. Lett.* vol. 96, no. 25, p. 252907, 2010.

- [12] R.J.W. Hill, D.A.J Moran, X. Li, H. Zhou, D. Macintyre, S. Thoms, A. Asenov, P. Zurcher, K. Rajagopalan, J. Abrokwah, R. Droopad, M. Passlack, I.G Thayne, "Enhancement-Mode GaAs MOSFETs with an In<sub>0.3</sub>Ga<sub>0.7</sub>As Channel, a Mobility of over 5000 cm<sup>2</sup>/Vs and Transconductance of over 475 μS/μm", *IEEE Electron Device Lett.*, vol. 28, no. 12, pp. 1080-1082, 2007.

- 13] E.J. Kim, L.Q. Wang, P.M. Asbeck, K.C. Saraswat, and P.C. McIntyre, "Border Traps in Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As (100) Gate Stacks and Their Passivation by Hydrogen Anneals," *Appl. Phys. Lett.* vol. 96, no. 1, p. 012906, 2010.