Hill, R.J.W. and Droopad, R. and Moran, D.A.J. and Li, X. and Zhou, H. and Macintyre, D. and Thoms, S. and Ignatova, O. and Asenov, A. and Rajagopalan, K. and Fejes, P. and Thayne, I.G. and Passlack, M. (2008) 1  $\mu$ m gate length, In<sub>0.75</sub>Ga<sub>0.25</sub>As channel, thin body n-MOSFET on InP substrate with transconductance of 737 $\mu$ S/ $\mu$ m. *Electronics Letters* 44:pp. 498-500.

http://eprints.gla.ac.uk/4144/

Deposited on: 6 May 2008

## 1 $\mu$ m gate length, In<sub>0.75</sub>Ga<sub>0.25</sub>As channel, thin body n-MOSFET on InP substrate with transconductance of 737 $\mu$ S/ $\mu$ m.

Richard J.W. Hill, Ravi Droopad, David A.J. Moran, Xu Li, Haiping Zhou, Douglas Macintyre, Stephen Thoms, Olesya Ignatova, Asen Asenov, Karthik Rajagopalan, Peter Fejes, Iain G. Thayne, Matthias Passlack.

*Abstract:* We report the first demonstration of implant-free, flatband-mode (FB) In<sub>0.75</sub>Ga<sub>0.25</sub>As channel n-MOSFETs. These 1µm gate length MOSFETs, fabricated on a structure with average mobility of 7720 cm<sup>2</sup>/Vs and sheet carrier concentration of  $3.3 \times 10^{12}$  cm<sup>-2</sup>, utilise a Pt gate, a high-κ dielectric (κ≈20), and a δ-doped InAlAs/InGaAs/InAlAs heterostructure. The devices have a typical maximum drive current (I<sub>d,sat</sub>) of 933µA/µm, extrinsic transconductance (g<sub>m</sub>) of 737 µS/µm, gate leakage (I<sub>g</sub>) of 40 pA, and on-resistance (R<sub>on</sub>) of 555 Ω.µm. The g<sub>m</sub> and R<sub>on</sub> figures of merit are the best reported to date for any III-V MOSFET.

*Introduction*: It is widely accepted that beyond the 22nm technology generation of the International Technology Roadmap for Semiconductors (ITRS), strained silicon may no longer deliver the performance required by the roadmap and that channel materials with better transport properties may be required [1]. Possible alternatives include Ge, GaAs, InGaAs, InAs, InSb, GaN, and perhaps others [2-8]. Recently published results from high performance flatband-mode [9] In<sub>0.3</sub>Ga<sub>0.7</sub>As channel enhancement-mode MOSFETs on GaAs substrate conclusively demonstrate that the historical issue of Fermi-level pinning at the GaAs/dielectric interface can be overcome

[10]. Although In<sub>0.3</sub>Ga<sub>0.7</sub>As n-channel MOSFETs are well suited to mobile RF applications, technological issues and intrinsic properties limit their ability to challenge aggressively scaled silicon nMOS devices for digital applications. For example, it is extremely demanding to reduce contact resistance to shallow In<sub>0.3</sub>Ga<sub>0.7</sub>As 2 dimensional electron gas (2DEG) layers below 300-400  $\Omega.\mu m$ , which is far in excess of the total parasitic series source drain resistance ( $R_{SD}$ ) requirement of 75  $\Omega.\mu m$  set by the ITRS for the 22nm technology generation [1]. In addition, Monte Carlo simulations have shown that In<sub>0.3</sub>Ga<sub>0.7</sub>As devices have limited drive current improvement over silicon below a gate length of 15nm, but that significant drive current benefit can be achieved by In<sub>0.75</sub>Ga<sub>0.25</sub>As channels due to reduced access resistance, increased source-injection velocity and a very high degree of ballisticity [11]. A further benefit of high indium content structures is the ability to form low resistivity, shallow source/drain contacts. As the indium concentration of InGaAs is increased, the Fermi-level pinning energy of a metal semiconductor contact moves from mid-gap towards the conduction band, reducing the barrier height and hence ohmic contact resistance [12]. For these reasons high indium concentration InGaAs channels are attractive candidates for nMOS devices beyond the 22 nm technology generation.

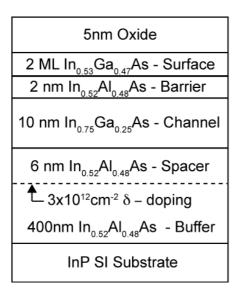

*Layer structure and device fabrication*: Material growth was carried out on a 2" semi-insulating InP substrate using a dual chamber system by a method similar to [13]. Fig. 1 gives the layer structure of the III-V MOSFET material, which consisted of the following layers; a 400nm lattice matched  $In_{0.52}AI_{0.48}As$  buffer, a  $3x10^{12}cm^{-2}$  Si  $\delta$  - doped plane, a 6 nm  $In_{0.52}AI_{0.48}As$  spacer, a 10nm

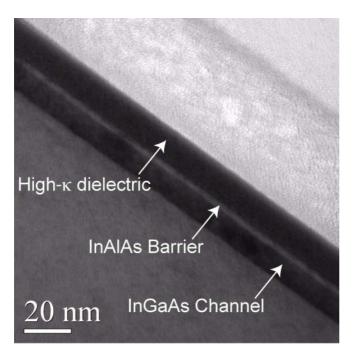

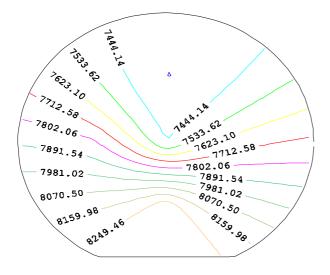

In<sub>0.75</sub>Ga<sub>0.25</sub>As channel, a 2nm In<sub>0.52</sub>Al<sub>0.48</sub>As barrier, a 2 monolayer (ML) In<sub>0.53</sub>Ga<sub>0.47</sub>As semiconductor surface layer, and a 5nm high- $\kappa$  metal oxide layer with  $\kappa \approx 20$ . A TEM cross-section of the layer structure can be seen in Fig. 2. The oxide and barrier layers have an equivalent oxide thickness (EOT) of 1.7 nm. To calculate the capacitance equivalent thickness (CET) the position of the charge in the channel must be considered. The charge centroid moves from the rear of the channel toward the front with increasing positive gate bias, so calculating an accurate CET is complex. As a first order approximation, half the channel thickness can be used to calculate the CET to be 3 nm. Fig. 3 gives a 2 dimensional map of mobility from contactless measurements of a wafer with a similar structure to that used for the devices. The average carrier concentration was  $3.3 \times 10^{12}$  cm<sup>-2</sup> and the average mobility was 7720 cm<sup>2</sup>/Vs. This is comparable to earlier reported data on similar layer structures [14].

As detailed in [10] a two-level wrap-around gate design (where the gate encircles the drain) was used to simplify the device process flow, removing the need for isolation. The gate length was 1µm and the source drain separation was 3µm. Both the gate and ohmic contacts were defined by direct write e-beam lithography and patterned by the lift-off method. The dielectric was removed by wet chemical etching prior to deposition of the ohmic contacts, which subsequently underwent rapid thermal annealing.

*Results*: Transmission line measurement (TLM) structures gave the contact resistance ( $R_c$ ) and sheet resistance ( $R_{sh}$ ) to be 78  $\Omega.\mu m$  and 195  $\Omega/sq$

respectively, which are the lowest III-V MOSFET parasitic access resistance components reported to date. Using a self-aligned process [15], which reduces the access length from 1 $\mu$ m to 50nm, the total parasitic access resistance (R<sub>SD</sub>) could be reduced to 165  $\Omega$ . $\mu$ m. This value is equivalent to current Si technology and could be improved to meet the ITRS 22nm target by further optimisation [1].

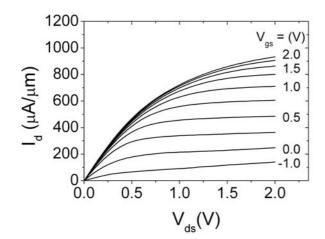

Fig. 4. gives typical output characteristics of a 1µm gate length device. These devices show excellent drive current ( $I_{d,sat}$ ) of 933µA/µm ( $V_{ds} = V_{gs} = 2 V$ ), peak transconductance ( $g_{m,max}$ ) of 737 µS/µm ( $V_{ds} = 2V$ ,  $V_{gs} = 0.275 V$ ) and  $R_{on}$  of 555  $\Omega$ .µm ( $V_{ds} = 0.05 V$ ,  $V_{gs} = 2 V$ ). The  $g_m$  and  $R_{on}$  values are the best reported to date for III-V MOSFETs, and considering the non-optimised layout and relaxed gate length, show the potential of this technology when scaled to the deca-nanometre regime. The electron saturation velocity ( $v_{sat}$ ) can be estimated using  $I_{dsat} \approx v_{sat}*q^*n_s$  to be  $1.8 \times 10^7$  cm/s, where q is the elementary charge, and  $n_s$  the sheet carrier density. This value is considerably greater than that found from  $In_{0.3}Ga_{0.7}As$  channels ( $1.2 \times 10^7$  cm/s) [16] confirming the improved transport properties of higher indium concentration channels. The difficulties in turning off the transistor are attributed to donor-type traps, mainly located in the lower portion of the band-gap at the semiconductor/oxide interface. In order to achieve a device quality interface, further significant improvements to the semiconductor/oxide interface are required.

*Conclusion:* We have demonstrated for the first time flatband-mode MOSFETs with high indium content in the channel. The excellent on-state

performance of these 1  $\mu$ m gate length devices (I<sub>d,sat</sub> = 933 $\mu$ A/ $\mu$ m, g<sub>m,max</sub> =

$737\mu$ S/ $\mu$ m and R<sub>on</sub> = 555  $\Omega$ . $\mu$ m) indicates the potential of this material system

and device architecture for post 22nm technology generation n-MOS solutions.

## Authors' affiliations:

R. Hill, D. Moran, X. Li, H. Zhou, D.Macintyre, S. Thoms, O. Ignatova, A. Asenov, and I. Thayne are with the Nanoelectronics Research Centre, University of Glasgow, Rankine Building, Oakfield Avenue, Glasgow, G12 8LT (e-mail: <u>r.hill@elec.gla.ac.uk</u>)

M. Passlack, R. Droopad, P. Fejes and K. Rajagopalan are with Freescale Semiconductor Inc., Tempe, AZ 85284 USA

## Figure captions:

Fig. 1 InP MOSFET layer structure.

Fig. 2 TEM cross section of InP MOSFET material with 15 nm thick oxide layer.

Fig. 3 Contactless mobility map of InP MOSFET wafer (in units of cm<sup>2</sup>/Vs)

Fig. 4 Output characteristics of a typical 1  $\mu$ m gate length InP MOSFET.

Figure 1

Figure 2

Figure 4

## References

- 1. International Technology Roadmap for Semiconductors. (2006). [Online]. Available: <u>http://www.itrs.net/Links/2006Update/2006UpdateFinal.htm</u>.

- 2. Datta, S., et al. 85nm gate length enhancement and depletion mode InSb quantum well transistors for ultra high speed and very low power digital logic applications. in IEDM Tech. Dig. 2005.

- 3. Kambayashi, H., et al., *Normally Off n-Channel GaN MOSFETs on Si Substrates Using an SAG Technique and Ion Implantation*. Electron Device Letters, IEEE, 2007. **28**(12): p. 1077-1079.

- 4. Thompson, S.E., et al., *Uniaxial-process-induced strained-Si: extending the CMOS roadmap*. Electron Devices, IEEE Transactions on, 2006. **53**(5): p. 1010-1020.

- 5. Kuzum, D., et al. Interface-Engineered Ge (100) and (111), N- and P-FETs with High Mobility. in IEDM Tech. Dig. 2007.

- 6. Chou, Y.C., et al. 0.1um In<sub>0.2</sub>Al<sub>0.8</sub>Sb InAs HEMT Low-Noise Amplifiers for Ultralow-Power Applications. in IEDM Tech. Dig. 2007.

- 7. Xuan, Y., et al. *High Performance submicron inversion-type enhancement-mode InGaAs MOSFETs with ALD Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub> and HfAlO as gate dielectrics.* in *IEDM Tech. Dig.* 2007.

- 8. Sun, Y., et al., *Enhancement-Mode Buried-Channel In<sub>0.7</sub>Ga<sub>0.3</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As MOSFETs With High-k Gate Dielectrics*. Electron Device Letters, IEEE, 2007. **28**(6): p. 473-475.

- 9. Passlack, M., et al., *Implant-Free High-Mobility Flatband MOSFET: Principles of Operation*. Electron Devices, IEEE Transactions on, 2006. **53**(10): p. 2454-2459.

- Hill, R.J.W., et al., Enhancement-Mode GaAs MOSFETs With an In<sub>0.3</sub>Ga<sub>0.7</sub>As Channel, a Mobility of Over 5000 cm<sup>2</sup> V/s, and Transconductance of Over 475 uS/um. Electron Device Letters, IEEE, 2007. 28(12): p. 1080-1082.

- 11. Kalna, K., et al., *Monte Carlo simulations of InGaAs nano-MOSFETs*. Microelectronic Engineering, 2007. **84**(9-10): p. 2150-2153.

- 12. Shen, T.C., G.B. Gao, and H. Morkoc, *Recent developments in ohmic contacts for III-V compound semiconductors*. Journal of Vacuum Science and Technology B: Microelectronics and Nanometer Structures, 1992. **10**: p. 2113-2132.

- Droopad, R., et al., *Compound semiconductor MOSFETs*. Microelectronic Engineering, 2007. 84(9-10): p. 2138-2141.

- 14. Droopad, R., et al.,  $In_{0.75}Ga_{0.25}As$  channel layers with record mobility exceeding 12,000  $cm^2/Vs$  for use in high-k dielectric NMOSFETs. Solid-State Electronics, 2006. **50**(7-8): p. 1175-1177.

- 15. Li, X., et al., A low damage Si<sub>3</sub>N<sub>4</sub> sidewall spacer process for self-aligned sub-100 nm III-V MOSFETs. Microelectronic Engineering. In Press, Accepted Manuscript.

- Rajagopalan, K., et al., *1um Enhancement Mode GaAs N-Channel MOSFETs With Transconductance Exceeding 250 mS/mm.* IEEE Electron Device Lett., 2007. 28(2): p. 100-102.