Kalna, K. and Roy, S. and Asenov, A. and Elgaid, K. and Thayne, I. (2000) RF analysis of aggressively scaled pHEMTs. In, Lane, W.A., Eds. *30th European Solid-State Device Research Conference.*, *11-13 September 2000*, pages pp. 156-159, Cork, Ireland.

http://eprints.gla.ac.uk/3017/

### RF analysis of aggressively scaled pHEMTs

K. Kalna, S. Roy, A. Asenov, K. Elgaid and I. Thayne

Device Modelling Group

Department of Electronics & Electrical Engineering,

University of Glasgow, Glasgow G12 8LT,

Scotland, United Kingdom

E-mail:kalna@elec.gla.ac.uk

URL: http://www.elec.gla.ac.uk/~kalna

#### **Abstract**

The effect of scaling on both the steady state and RF performance of pseudomorphic high electron mobility transistors is extensively studied as these devices shrink to deep decanano dimensions. Investigation of appropriately scaled devices with gate lengths of 120, 70, 50, and 30 nm is performed. The devices exhibit a significant improvement in both transconductance and RF response as gate length is reduced, although device parasitics become a limiting factor.

### 1. Introduction

Pseudomorphic high electron mobility transistors (pHEMTs) with low indium content channels and  $0.2-0.1~\mu m$  channel lengths are currently considered to be conventional devices. Nevertheless, their performance can be enhanced by proper scaling. In this work, we extensively study possible improvements in the performance of pHEMTs as they are scaled to deep decanano dimensions. We have considered a set of pHEMTs appropriately scaled in both lateral and vertical directions with gate lengths of 120, 70, 50, and 30 nm. This is the first phase of a large (£ 2.6M) ex-

perimental programme in Glasgow aiming to establish Roadmap benchmarks for highspeed III-V devices.

## 2. Finite element Monte Carlo simulator

The finite element Monte Carlo device simulator (MC/H2F) has been used [1] to investigate electron transport properties in the pHEMTs. The simulator uses quadrilateral elements to depict a complex geometry of the pHEMTs and accurately calculates electrostatic effects caused by the gate and recess geometry as well as the surface potential pinning. The Monte Carlo module includes electron scattering with polar optical phonons, inter- and intra-valley optical phonons, non-polar optical, and acoustic phonons; and ionized and neutral impurity scattering. In addition, alloy scattering and strain effects [2] are considered for the InGaAs channel of the pHEMT. All scattering rates are calculated with a form factor (the overlap integral) proposed by Matz [3]. This form factor can be written as

$$F = \frac{(1 + \alpha E)(1 + \alpha' E') + \frac{1}{3} \alpha E \alpha' E'}{(1 + 2\alpha E)(1 + 2\alpha' E')},$$

(1)

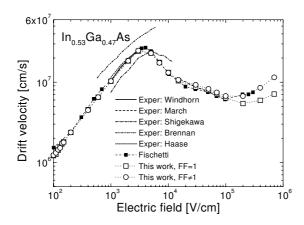

Figure 1. Simulated and experimentally obtained drift velocity versus applied electric field for  $ln_{0.53}Ga_{0.47}As$ .

assuming that an electron with an initial energy E attains a final energy E' after scattering and that  $\alpha$  and  $\alpha'$  are the non-parabolicity parameters in the initial and final band, respectively.

This enhancement of the analytical band model for III-V materials allows us to extend the regime over which we can confidently predict electron transport properties up to an electric field of  $200~\rm kV/cm$ . The drift velocity versus electric field simulation of Fig. 1 clearly illustrates that using the form factor (1) can substantially improve agreement with experimental data as well as with the full band simulations of Fischetti [4] for bulk  $In_{0.53}Ga_{0.47}As$  at high electric fields. Note that the analytical band model is expected to break down at very high electric fields (>  $200 - 300~\rm kV/cm$ ), at which point full band models must be used.

# 3. Effect of scaling on pHEMT performance

The pHEMT devices studied here have a T-shaped gate [5] and InGaAs channel with the indium content x = 0.2.

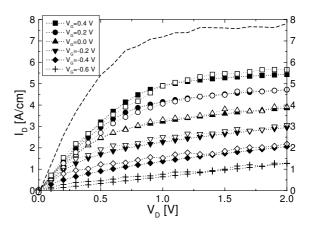

Figure 2. I-V characteristic of the calibrated pHEMT with a gate length of 120 nm. Full symbols are experimental data of the drain current versus the drain voltage for several fixed gate voltages. Open symbols represent a MC simulation when external resistances of the drain and source are included. The I-V characteristic for an intrinsic device (dashed line) is shown for comparison, for a gate voltage of 0.4 V.

The whole scaling investigation is based on careful calibration of the MC simulations against an 120 nm gate length pHEMT designed and fabricated by the Nanoelectronics Research Centre at the University of Glasgow. The simulated I-V characteristics, obtained directly from MC/H2F, represent the behaviour of the intrinsic device. To compare this with experimental data the contact resistances of the source and drain [6] are included in the I-V curves at a post-processing stage. In this case  $R_S =$  $5.22 \ \Omega, R_D = 0.6 \ \Omega \ \text{and} \ R_G = 2.4\Omega.$ The final I-V characteristics (open symbols in Fig. 2) for gate voltages from -1.0 Vto 0.4 V are in extremely good agreement with the experimental data (full symbols in Fig. 2). The result for an intrinsic device is shown by the dashed line for a gate voltage of 0.4 V only.

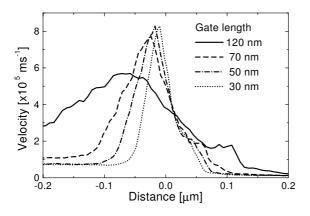

Figure 3. Average velocities along the InGaAs channel for a set of the scaled pHEMTs when drain and gate voltages are 1.5 V and 0.0 V, respectively

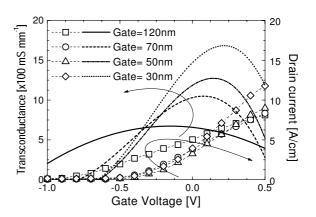

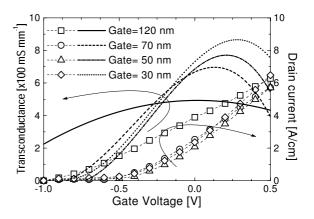

Fig. 3 shows the rapid increase in average channel velocity as pHEMT gate length is scaled from 120 to 70 nm. This improvement saturates with further scaling in the 50 and 30 nm devices, with continued device improvements resulting solely from the decreasing source-drain distance. The drain current and the transconductance as a function of gate voltage are plotted in Fig. 4 for intrinsic devices. Fig. 5 illustrates the effect of the external contact resistances on the device performance, assuming that the value of these resistances remains unchanged in the scaling process. Influence of the external resistances on the device performance (both on the drain current and the transconductance) becomes increasingly important with the reduction in device scale.

## 4. RF Analysis

The MC/H2F simulator is also used to carry out device RF analysis. Step voltage changes are applied to the gate, and then to the drain contacts. Transient responses are recorded for a period of 6.0 ps using a mod-

Figure 4. Transconductance and drain current versus the gate voltage for intrinsic devices of the scaled pHEMTs.

Figure 5. Transconductance and drain current versus the gate voltage for scaled pHEMTs with external resistances included.

ified Ramo-Shockley approach [7] reducing the effects of statistical noise over purely superparticle counting methods. Structure and doping dependent THz oscillations in device drain currents (possibly due to plasma oscillations in the channel or heavily doped regions) may mask the detailed form of the transients and multiple traces are averaged to define the response. Complex *y*-parameters are derived by Fourier analysis of the terminal currents, and the intrin-

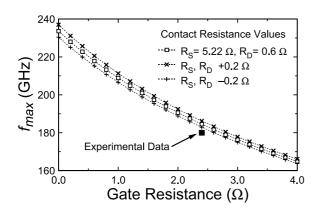

Figure 6. Maximum frequency of oscillation,  $f_{max}$  as a function of gate, source and drain resistances, for the calibrated pHEMT with gate length 120 nm. Open squares represent a simulation with the same  $R_S$ ,  $R_D$  as measured experimentally.

sic cut-off frequency,  $f_T$ , is extracted by solving  $\log [G_C(\log f)] = 0$  where  $G_C =$  $dI_d/dI_q$  is the current gain expressed as a function of y-parameters. To extract the intrinsic maximum frequency of oscillation,  $f_{max}$ , the y-parameters are transformed into s-parameters.  $f_{max}$  is then extracted by solving  $\log [MAG (\log f)] = 0$  where MAG is the maximum available gain. After steady state calibration of the MC simulation noted above, extraction of intrinsic RF results require no further fitting parameters. Transformation to z-parameter form allows the addition of external impedances such as contact resistance, and thus the estimation of realistic  $f_T$  and  $f_{max}$  values. shows the sensitivity of  $f_{max}$  to parasitic resistances neighbouring those measured for the 120 nm pHEMT, and indicates close agreement with experiment. The simulated intrinsic  $f_{max}$  for this device is 810 GHz. Assuming external resistances remain unchanged as the device scales to 70 nm, an  $f_{max}$  of 248 GHz is obtained. However, due

to the limiting effects of the external parasitics (and in part due to narrowing of the transconductance peak, reducing the span of useful high transconductance), continued scaling to 50 and 30 nm fails to show further improvement.

- S. Babiker, A. Asenov, J. R. Barker, and S. P. Beaumont, "Finite element Monte Carlo simulation of recess gate compound FETs", Solid St. Electron. 39 (1996) pp. 629-635.

- [2] Ch. Köpf, H. Kosina and S. Selberherr, "Physical models for strained and relaxed GaInAs alloys: band structure and low-field transport", Solid St. Electron. 41 (1997) pp. 1139-1152.

- [3] D. Matz, "Effects of nonparabolicity on non-ohmic transport in InSb and InAs", Phys. Rev. **168** (1968) pp. 843-844.

- [4] M. V. Fischetti, "Monte Carlo simulations in technologically significant semiconductors of the diamond and zinc-blende structures-part I: Homogeneous transport", IEEE Trans. Electron Devices 38 (1991) pp. 634-648.

- [5] S. Babiker, A. Asenov, S. Roy, and S. P. Beaumont, "Strain engineered pHEMTs on virtual substrates: a Monte Carlo simulation study", Solid St. Electron. 43 (1999) pp. 1281-1288.

- [6] S. Babiker, A. Asenov, N. Cameron S. P. Beaumont, "A simple approach to include external resistances in the Monte Carlo simulation of MESFETs and HEMTs", IEEE Trans. Electron Devices 43 (1996) pp. 2032-2034.

- [7] H. Kim, H.S. Min, T.W. Tang, Y.J. Park, "An Extended Proof of the Ramo-Shockley Theorem", Solid St. Electron. 43 (1991) p 1251.