Zhao, J., Parvizi, R., Ghannam, R., Law, M.-K., Walton, F., Imran, M. A. and Heidari, H. (2023) Self-powered implantable CMOS photovoltaic cell with 18.6% efficiency. IEEE Transactions on Electron Devices, 70(6), pp. 3149-3154.

Copyright © 2023 IEEE. Reproduced under a <u>Creative Commons Attribution 4.0</u> <u>International License</u>.

For the purpose of open access, the author(s) has applied a Creative Commons Attribution license to any Accepted Manuscript version arising.

https://eprints.gla.ac.uk/296706/

Deposited on: 18 April 2023

$Enlighten-Research \ publications \ by \ members \ of \ the \ University \ of \ Glasgow \ \underline{https://eprints.gla.ac.uk}$

1

2 3

8

9

10 11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53 54

55

56

57

58

59 60

# Self-Powered Implantable CMOS Photovoltaic Cell with 18.6% Efficiency

# Jinwei Zhao, *Member, IEEE*, Roghaieh Parvizi, Rami Ghannam, *Senior Member, IEEE*, and Man-kay Law, *Senior Member, IEEE*, Finlay Walton, *Member, IEEE*, Muhammad Ali Imran, *Senior Member, IEEE* and Hadi Heidari, *Senior Member, IEEE*

Abstract— Harvesters for implantable medical applications need to generate enough energy to power their loads, but their efficiency is reduced when implanted under tissue. Conventional PV cell harvesters made with CMOS technology stack cells in series, which raises output voltage but lowers power conversion efficiency. Additionally, it is difficult to assess harvester performance prior to fabrication. To address these challenges, we developed a novel parallel PV cell configuration that fully utilizes all triple-well diodes and respond efficiently to near-infrared light. Using an optimized structure, the PV cells were fabricated through standard TSMC 65 nm CMOS technology, achieving an efficiency of 18.6%, open circuit voltage of 0.45 V, and short circuit current of 1.9 mA cm<sup>-2</sup>. These results confirm the ability of the device to generate sufficient energy even when implanted beneath tissue. Multiphysics Finite Element Modelling (FEM) was used to optimize the stacking structure of the CMOS PV cell, and experimental results showed a successfully delivered power density of 1.2 mW cm<sup>-2</sup> (single cell 1.04 mm<sup>2</sup>) when placed 2 mm below porcine skin. Different array configurations of six PV cells were also experimentally studied using external wires switching, demonstrating the flexibility of the PV array in delivering different output energy for various implantable devices.

*Index Terms*—Implantable Device, Photovoltaic Cell, CMOS, Energy Autonomous, Efficiency, Human Skin.

## I. Introduction

Implantable medical devices are becoming more prevalent in healthcare, but they face the challenge of providing stable and sustainable energy for their electronic components without relying on batteries with limited lifetimes [1]. Conventional batteries have a lifespan of 7-10 years in cardiac pacemakers and 3-5 years in deep brain stimulators [2]. Power harvesting methods, such as piezoelectric nanogenerators, RF harvesters, thermal generators, and photovoltaic (PV) cells, can extend the lifespan of implantable devices. PV cells have high energy conversion efficiency, are a renewable power source, and have high output power [3]. However, the penetration of optics into skin results in the absorption and scattering of some light energy, limiting the depth of implantation, and necessitating the use of bulkier devices [4]. Research by AN Bashkatov in 2011 found that biological tissues have two optimal windows of optical transparency in the near-infrared region, at 650-950 nm and 1000-1350 nm [5]. To reduce the loss of light energy in these tissues, PV cells should be designed to efficiently respond to the NIR light (need high quantum efficiency). Additionally, to facilitate surgical implantation, PV cells are usually limited in size to the millimeter scale, and the power source is kept at low-flux near-infrared to prevent overheating. Implantable PV cells are more affected by limitations such as shunt resistance and recombination loss, as compared to larger-scale PV devices [6].

The standard complementary metal-oxide semiconductor (CMOS) technology is commonly used to fabricate small-scale implantable PV cells, as it allows for the monolithic combination of integrated photodiodes (harvester) and multifunction circuits (application load) in biomedical implantable devices [7]. This approach is considered a promising method for creating implantable PV cells. However, in implantable PV cells using the triple-well technology for designing the junction diodes by deep-N-wells (DNWs) has limitations in terms of shunt conductance and surface recombination. This is because the use of low-flux NIR (near-infrared) and optic transmittance is restricted by the metal contact shading. The low shunt resistance can result in power loss caused by the flow of alternate current from the light-generated current. In contrast, low series resistance plays a role in avoiding carrier recombination, which is typically around 80~100 of ohm/sq under normal lighting conditions. Some researchers have proposed the back-illumination solution to overcome the limitation of optical shading [6]. To enhance the optical performance of a device by reducing the impact of metal tracks on the illumination pathway or electrically isolating on-chip cells, various methods are employed such as back-illumination approach [7], localized substrate removal [8], oxide trenches [9], and oxidized porous silicon [10]. However, the implementation of these methods requires additional postprocessing steps, such as substrate thinning or modification, which can be time-consuming and laborious. Additionally, the oxide used for isolation can also isolate the P-sub/DNW diode, which is considered the most efficient in the NIR region [10].

This work was supported by grant EP/R511705/1 from EPSRC, UK and the European Union's Horizon 2020 Hybrid Enhanced Regenerative Medicine Systems (HERMES) project (GA n. 824164).

J. Zhao, Dr. R. Parvizi, Dr. R. Ghannam, Prof. M. Imran and Dr. H. Heidari are with the James Watt School of Engineering, University of Glasgow, Glasgow, G12 8QQ UK (Hadi.Heidari@glasgow.ac.uk).

Prof. M. Law is with the State Key Laboratory of Analog and Mixed-Signal VLSI, Faculty of Science and Technology, University of Macau, Macau, China (mklaw@um.edu.mo).

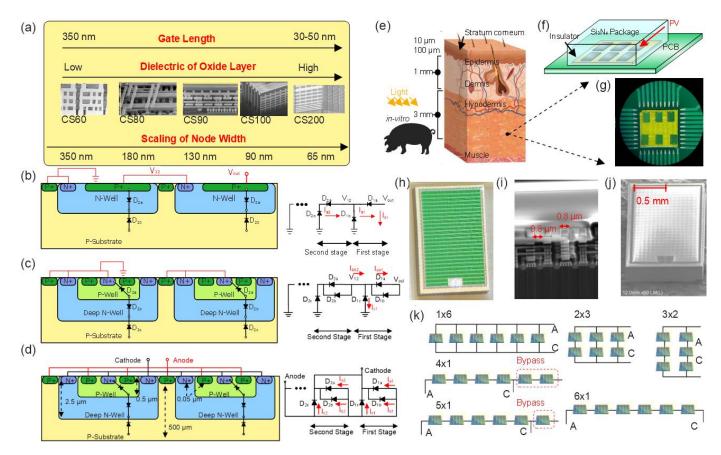

Fig 1. (a) Parameters of CMOS technology scaling evolution from 350 nm to 65 nm. (b) Stacking schematic and equivalent circuit of double-well 0.35 µm CMOS technology by M. K. Law et al. [12]. (c) Stacking schematic and equivalent circuit of triple-well 0.25 µm CMOS technology by G. Hong et al. [13]. (d) is the proposed work in this paper. (e) is the pork skin structure applied in FEM simulation and (f) is the schematic of the encapsulation and PCB wire bonding. (g) Developed configuration schematic and equivalent circuit of triple-well 65 nm CMOS technology in this work. Device structure of the implantable PV cells array. (h) Magnified image of the implantable PV cell in CMOS 65 nm technology. (i, j) magnified images taken by microscope and SEM of a single cell, respectively. (k) 6 types of configurations; 1×6, 2×3, 3×2, 4×1, 5×1 and 6×1.

Another promising technique to address the issue of optical shading is to reduce the width of the metal finger placement. This leads to a faster movement of electron-hole current in the electrodes, and thus a higher parasitic capacitance [11]. Turning the point to recombination and shunt resistance, CMOS PV designs should incorporate thin epi layers. These layers are more easily depleted by smaller bias voltage due to their lower doping concentration. Also, in a thin substrate, majority of photogenerated electrons recombine before diffusing into the depletion region, as the minority carrier recombination rate is faster in thinner substrate [11]. In addition, a high dielectric constant can help reduce surface recombination, which is often improved by scaling in CMOS technology (as shown in Fig. 1a).

Various designs of CMOS PV cells have been explored to achieve higher output voltage, with some designs bypassing the use of the DNW photodiode [11-13]. However, conventional DNW PV cells often rely on stacking cells in series, which may increase output voltage but decrease power conversion efficiency due to underutilization of diodes. Previous studies have shown that an N+/PW (heavy n-doped/p-well) and DNW/PS (deep n-well/p-substrate) connected in series can achieve 5.9% efficiency with PW/DNW (p-well/deep n-doped well) bypassed, while three diodes in parallel can improve efficiency to 21.9%, indicating significant potential for

improvement [14]. Furthermore, assessing the performance of such energy harvesting devices before fabrication is challenging. In this research, we introduce an optimized DNW PV cell structure with specific features such as a narrow finger place width, thin epi layer, and parallel connection of three junction diodes to develop implantable energy harvesting devices. We utilized 65 nm CMOS technology to achieve a low sheet series resistance of 8 ohm/sq, a shunt sheet resistance of 15m Ohm/sq, a thin epi layer of 3 um, a narrow finger place width of 0.8 um, a metal finger width of 0.8 um, and a Si3N4 encapsulation, resulting in a high quantum efficiency (OE) of 65% with responsivity of 0.4 A/W, and an overall power conversion efficiency of 18.6%. Our modifications ensure that the implantable medical device can continue to generate sufficient energy to power the device even when placed under tissue.

## II. CMOS PV CELL STRUCTURE AND DESIGN

Fig. 1(b), 1(c) and 1(d) show three configurable topologies to connect three served photodiodes and produce an implantable PV cell. The first topology (shown in Fig. 1(b)) is proposed by M. K. Law et al. 2011, [12] which was fabricated using double-well 0.35  $\mu$ m CMOS technology. The power conversion efficiency of the stacking photodiode in this technique can be approximated using [13]:

1 2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29 30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58 59 60

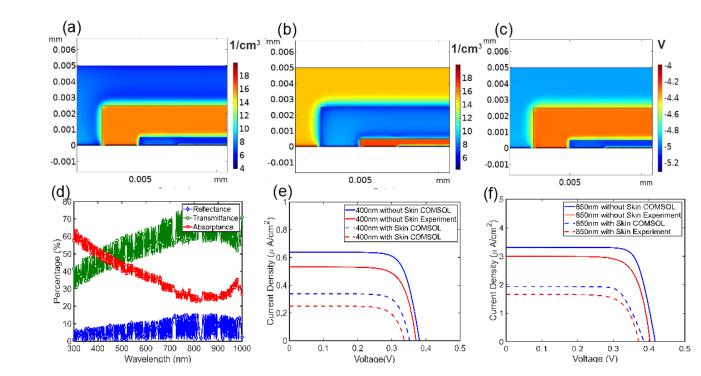

Fig 2. (a) the electron concentration in the PV cell modelling with a setup of uniform doping technique. (b) shows the hole concentration in the PV cell modelling with a setup of uniform doping technique. (c) shows the electrical field of the PV cell related to the depth gradient. (d) the optical performance of the multilayer structure in Figs. 1(b) and 1(c), which are Reflectance (R), Transmittance (T) and Absorptance (A). (e) the JV characteristics of the PV cells with or without skin and encapsulation layer on the top in wavelength 400 nm (white light), where the COMSOL results are compared with experiment results. (f) the JV characteristics of the PV cells with or without skin and encapsulation layer on the top in wavelength 808 nm (NIR light), where the COMSOL results are compared with experiment results.

$$K > 1 + \alpha \tag{0.1}$$

$$\eta = \eta_0 \times N \frac{K-1}{K^N - 1} \tag{0.2}$$

where K is the area ratio of the PV cell,  $\alpha$  is the ratio of the leakage photocurrent ( $\alpha = I_{bN}/I_{aN}$ ),  $\eta$  is the total efficiency while  $\eta_0$  is the efficiency of the first stage, and N is the number of stages [13]. The efficiency decreases with a large K value, so that K should be minimised. Nevertheless, K is limited by  $1+\alpha$ . In this case,  $\alpha$  should be minimised to obtain smaller K. To be specific, I<sub>bN</sub> should be minimised and I<sub>aN</sub> should be maximised. The second configuration technique in Fig. 1(c) is applied to minimise  $\alpha$  (I<sub>abN</sub>/I<sub>cN</sub>), which was fabricated using 0.35 µm CMOS triple-well technology [13]. In the triple-well technology, a DNW/PW (D<sub>Nb</sub>) diode was connected in parallel with PW/N+ ( $D_{Na}$ ), which increases the current  $I_{abN}$ . The introduction of DNW below NW means that more light is attenuated before reaching the P-sub/DNW (D<sub>Nc</sub>) layer, which reduces the amount of photogenerated current [13]. One advantage of the first and second techniques is increasing the output voltage of PV cells, which is convenient to sustain MOSFETs in energy harvesting circuits on the same chip. Besides, one P-sub/DNW diode in the final stage is bypassed, which means the diodes are not fully used.

The third configurable topology is connecting three photodiodes in parallel (Fig. 1(d)) to optimize the output current as the output current of the triple well photodiodes is the sum of the current of the three individuals. In comparison, the output voltage of the three photodiodes is the same as the smallest voltage from three diodes. Compared with all three configuration techniques, all three photodiodes were connected in parallel to make the whole device fully illuminated. The conventional method of stacking PV cells on the same substrate results in some diodes being bypassed, leading to a decrease in efficiency. In contrast, this proposed approach utilizes wire bonding technology to separate the PV cells and avoid the need for a shared substrate. Next, the anodes and cathodes of the unit cell in Fig. 1(d) were connected to the anode pad and cathode pad. The PV cells were connected to a floating voltage, while the anode and cathode were connected to the external circuit directly instead of connecting the P-substrate to the ground. However, the output voltage of the third technique is limited by  $V_{oc}$  of  $D_{Nc}$ . In previous research, the researchers apply the similar parallel connection technique, but their connection exclude N+/PW diode, which means the power is limited and the chip area is not fully used. Some work like [7] and [11] also show the FEM analysis but the relevant model was not verified and only the electric field was shown. However, the other electric and optical results are equally significant for photovoltaic cell study. The Fig. 1(e) shows the skin model applied in simulation, Fig. 1(f) shows the device stacking and encapsuling structure and Fig. 1(g) shows the Chip-on-Board (COB) layout. Layout design of the implantable PV cell in CMOS 65 nm technology was shown in Fig. 1(h) as well as the magnified images taken by a microscope and scanning electron microscopy (SEM) scanned in Fig. 1(i) and 1(j), respectively. The SEM images clearly shows the geometry of the CMOS PV cells. Additionally, different array configurations of six PV

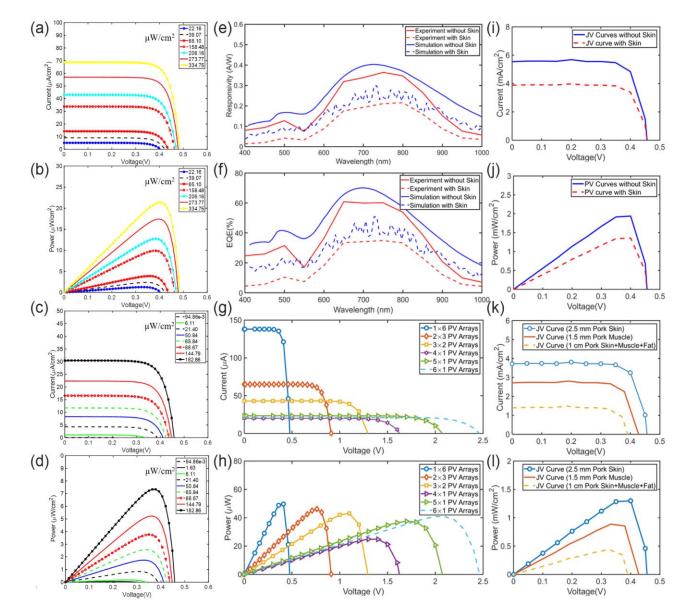

Fig 3. (a) The JV characteristic by illuminating the PV cell with Lens: Motic ELWD 10×/0.28. (b) The output power density (c) The JV characteristic by illuminating the PV cell with Lens 2: Motic ELWD 2×/0.055 related to Fig. 3(a). (d) The output power density related to Fig. 3(b). (e) The responsivity of the PV cell only and implanted PV cell tested by sweeping wavelength from 400 nm to 1100 nm in Newport 69935. The results compared with simulation. (f) The EQE calculated from the data in Fig. 3(e) and compared with simulation results. (g) JV characteristics of different PV array configurations. (h) P-V curve of the different PV array configurations. (i) JV curves of the single PV cell with skin and without skin by being illuminated by 808 nm M9095I laser diode. (j) P-V curves of the single PV cell under skin and cell only by being illuminated by 808 nm M9095I laser diode. (l) P-V curves under different skin layers.

cells were also experimentally tested by exploiting external wires switching, as shown in Fig.1(k) to achieve different output energies for different tasks.

#### III. Result and Discussion

#### A. Simulation Results and Discussion

The electron and hole concentrations are shown in Figs. 2(a) and 2(b). In terms of electron concentration, minority carrier concentration is shown in the PS, PW and P+ regions. We can also predict the concentration of minority carriers in the N+ and DNW regions. For device modelling, a uniform doping profile was assumed. Fig. 2(c) shows the electric field in the junctions according to the depth gradient, which is from 4 V to 5.2 V. The high electrical field inside the PV cell can improve the ability to separate the electron-hole pairs when the PV cell is illuminated with incident light and photons are absorbed. Fig. 2(d) shows the optical reflectance (R), transmittance (T) and absorbance (A) from the multilayer structure shown in Fig. 2(a), which consists of 4.1 mm porcine skin, 1 mm Si<sub>3</sub>N<sub>4</sub> encapsulation, 2 mm air and a 500  $\mu$ m Si substrate. Accordingly, maximum transmittance (70%) occurred at 808 nm, whereas peak absorbance (80%) occurred in the ultraviolet region (300 nm).

Moreover, Fig. 2(e) shows the current density-voltage (J-V) characteristics of the single PV cell model (forward biasing from 0 V to 0.6 V), which yields a  $V_{oc}$  of 0.38 V and a  $J_{sc}$  of 0.62  $\mu$ A cm<sup>-2</sup> for a 400 nm incident light source with a P<sub>in</sub> of

16 17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

58 59 60

|                                                     | TABLE I.   GEOMETRY AND DOPING PROFILE OF THE IMPLANTABLE PV CELL. |                 |                   |                   |                 |                   |               |  |

|-----------------------------------------------------|--------------------------------------------------------------------|-----------------|-------------------|-------------------|-----------------|-------------------|---------------|--|

|                                                     | This<br>Work                                                       | Z. Chen<br>[14] | S.Ayazian<br>[17] | T. Tokuda<br>[18] | G. Hong<br>[13] | A. Ahnood<br>[19] | L. Lu<br>[16] |  |

| Efficiency (without skin)                           | 18.6%                                                              | 21%             | 23%               | 0.25%             | 4.7%            | 17%               | 2.14%         |  |

| $P_{in}$ (mW/cm <sup>2</sup> )                      | 4.6-10                                                             | 113             | 50                | 9.6               | 60              | 57                | 200           |  |

| λ (nm)                                              | 808                                                                | 850             | 550               | 400-750           | 860             | 980               | 780           |  |

| tskin (mm)                                          | 4                                                                  | 4.5             | 3                 | -                 | -               | 0.5               | 2-4           |  |

| Encap.                                              | Si <sub>3</sub> N <sub>4</sub>                                     | -               | -                 | -                 | Resin           | Diamond           | PLGA          |  |

| Tech.                                               | 65 nm                                                              | 180 nm          | 180 nm            | 250 nm            | 350 nm          | SILVER            | SOI           |  |

| V <sub>out</sub> (V) without skin                   | 0.45                                                               | 0.53            | 0.42              | 1.25              | 0.45            | 0.64              | 0.4           |  |

| Vout (V) Arrays without skin                        | 2.5                                                                | -               |                   | 1.6               | 3.92            | -                 | 4.84          |  |

| J <sub>sc</sub> (mA/cm <sup>-2</sup> ) without skin | 5.6                                                                | 5.77            | 2.2               | 0.026             | -               | 510               | 4.34          |  |

| FF without skin                                     | 0.64                                                               | 0.81            | 0.55              | 0.57              | -               | 0.66              | 0.73          |  |

| Pout (mW/cm <sup>-2</sup> ) without skin            | 1.61                                                               | 0.64            | 0.508             | 0.024             | -               | 216               | 1.26          |  |

| Pout (mW/cm <sup>-2</sup> ) under skin              | 1.2                                                                | 0.18            | 0.05              | -                 | -               | 37.38             | 1.07          |  |

<sup>a</sup> PLGA (Poly Lactic-co-Glycolic Acid)

90 µW cm<sup>-2</sup>. However, after implanting the PV cell under the skin, encapsulation, and air layers, the Voc and Jsc dropped to 0.35 V and 0.35 µA cm<sup>-2</sup> respectively. NIR light was mostly used to power the implantable PV cells because of its ability to penetrate skin. In this case, we exposed the PV cells to an 808 nm light source at normal incidence, which delivered 100  $\mu$ W mm<sup>-2</sup> of power. The J-V curves shown in Fig. 2(f) demonstrate improved performance, where Voc and Jsc were improved to 0.42 V and 3.4 µA cm<sup>-2</sup>. After implanting the PV cells under skin and the encapsulation layer, the Voc and Jsc reduced to 0.38 V and 1.9 µA cm<sup>-2</sup>. Based on these results, PV cells illuminated with NIR light yield better electrical performance in comparison to white light with skin layers or without skin layers. The simulation results of EQE will be discussed in Section III(B).

### B. Experimental Results and Discussion

Herein, the Current Density vs. Voltage (JV) characteristics and quantum efficiency were tested using a digital power meter (Newport Optical Power Meter 2936-C r®) and Newport power supplier and filter (Newport 69935 platform). The Voc shows a variation from 0.35 V to 0.6 V if the incident optical power is increased from 200 nW cm<sup>-2</sup> to 1000 µW cm<sup>-2</sup>, (Figs. 3(a) to 3(d)). Naturally, the  $J_{sc}$  also increases from 345 nA cm<sup>-2</sup> to 210  $\mu A$  cm<sup>-2</sup> with increasing incident optical power. The efficiencies of the PV cells when illuminated using lens 1 and lens 2 are 8.64% and 6.12% under 530 nm light 1000 µW cm<sup>-2</sup>. This degradation in performance is attributed to the temperature change on the Si PV cell since the illumination area and power density are different for both lenses.

46 Figs. 3(e) and 3(f) demonstrate the responsivity and EQE of 47 the PV cells. Our PV cells are most responsive at a wavelength 48 of 750 nm, since EQE was 58% and Responsivity was 0.37 A 49 W-1. However, the peak EQE was attenuated to 32% under the skin. These results agree with our simulations modelling which 50 predicts an EQE of 65% and Responsivity of 0.4 A W<sup>-1</sup>. This 51 value drops to 40% EQE due to tissue losses. Our simulated 52 data values are higher since the CMOS fabrication process 53 involved depositing a SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> passivation layer on top 54 of our devices, which were not included in our simulations. The 55 properties and geometry of these two surfaces layers were not 56 available to us. 57

The diode is placed from 2 mm to 4 mm above the PV cell

COB surface, which gives a 4.6 mW cm<sup>-2</sup> to 10 mW cm<sup>-2</sup> input power to the PV cell. The J-V characteristic curve is shown in Fig. 3(i), where the PV cell yields  $J_{sc}$  of 5.6 mA cm<sup>-2</sup>,  $V_{oc}$  of 0.45 V and Fill Factor (FF) of 0.61. After placing the PV cell under porcine skin, J<sub>sc</sub> was attenuated to 3.8 mA cm<sup>-2</sup>. Fig. 3(j) shows the P-V curve, where Pout decreased from 1.86 mW cm<sup>-2</sup> (in air) to 1.2 mW cm<sup>-2</sup> under skin. Correspondingly, PV cell efficiencies were 18.6% and 12% for an incident power intensity of 8.6 mW cm<sup>-2</sup>.

Fig. 3(g) and 3(h) shows the J-V and P-V characteristic curve of different PV cell array configurations. The configurations were switched using external wires, and the structure is shown in Fig. 1(k). We arranged our six PV cells in the following configurations:  $1 \times 6$ ,  $2 \times 3$ ,  $3 \times 2$  and  $6 \times 1$ . We investigated the output J-V and P-V characteristics of these configurations, as well as the output characteristics of fewer PV cells, namely the  $4 \times 1$  and  $5 \times 1$  configurations. Our motivation was to demonstrate the flexibility of our PV array in delivering different output energy for various implantable devices. Our PV cell arrays were characterized using an ABET SunLite Solar Simulator [15]. Maximum output current was achieved using the 1×6 array, which was 144 µA. Moreover, since connecting more PV cells in series helps boost the output voltage, highest output voltages were achieved using the  $6 \times 1$  and  $1 \times 6$ configurations (2.5 V). With an energy reservoir, the  $1 \times 6$  array can also be used to speed up the charging time for low-voltage loads. Fig. 3(k) and Fig. 3(l) show the electrical characteristics by placing a single PV cell under different skin layers (2.5 mm porcine skin, 1.5 mm porcine muscle and 1 cm porcine skin+muscle+fat).

The experimental results show 18.6% efficiency using an 808 nm NIR laser diode. In comparison to using a 530 nm light source, the output voltage decreases for 808 nm light due to the parasitic resistance of the wire connection and the bonding in the PCB. Table I, [13, 16-19] shows a comparison between the performance of our PV cells and the literature. Our fabricated CMOS cells yield the highest power conversion efficiencies in comparison to previously published data while the output voltage is 0.45 V, which is lower than some of the stacked PV cells in [14] and [13], and the power conversion efficiency without skin shows similarly. However, the delivered power under the skin is better than the literature review considering the input power density is only 10 mWcm<sup>-2</sup>, while it is lower

[7]

than the one fabricated by SILVER tech. Furthermore, since we had six PV cells that were wired-bonded on a PCB, the output voltage can be changed from 0.45 V to 2.5 V by reconfiguring the PV cell array. The implanted PV cells' active areas are 1.04 mm<sup>2</sup> (single) and 6.24 mm<sup>2</sup> (Arrays).

## IV. CONCLUSION

In summary, the challenges of implantable medical applications requiring harvesters with sufficient energy generation capacity have been addressed. The conventional approach of stacking PV cells in series leads to degraded power conversion efficiency due to underutilization of the Psub/DNW diode and implanting under tissue further compromises efficiency. We proposed a novel parallel PV cell configuration that fully utilizes all triple-well diodes, resulting in more efficient energy generation. Our experimentally verified FEM model can aid in designing better and more efficient PV cells for implantable applications. It results in a high quantum efficiency (QE) of 65% with responsivity of 0.4 A/W, and an overall power conversion efficiency of 18.6%. We also demonstrated that a reconfigurable PV connection can produce a broad range of output voltages (0.45-2.5V) and achieved a power conversion efficiency of 12% under 2 mm porcine skin. This promising result suggests that implanted PV cells can be used to power a wide range of implantable medical applications, such as pacemakers, retinal stimulators, and hearing aids. This study provides evidence that CMOS technology can be used to improve the efficiency of implanted PV cells and that supply voltage can be adjusted or reconfigured according to different applications.

#### REFERENCES

- H.-J. Yoon, and S.-W. Kim, "Nanogenerators to power implantable medical systems," *Joule*, vol. 4, no. 7, pp. 1398-1407, 2020. DOI: 10.1016/j.joule.2020.05.003

- B. Shi, Z. Li, and Y. Fan, "Implantable energy-harvesting devices," *Advanced Materials*, vol. 30, no. 44, pp. 1801511, 2018. DOI: 10.1002/adma.201801511

- [3] J. Zhao, R. Ghannam, K. O. Htet, Y. Liu, M. k. Law, V. A. Roy, B. Michel, M. A. Imran, and H. Heidari, "Self-Powered implantable medical devices: photovoltaic energy harvesting review," *Advanced healthcare materials*, vol. 9, no. 17, pp. 2000779, 2020. DOI: 10.1109/ICECS49266.2020.9294875.

- [4] X. Huang, L. Wang, H. Wang, B. Zhang, X. Wang, R. Y. Stening, X. Sheng, and L. Yin, "Materials strategies and device architectures of emerging power supply devices for implantable bioelectronics," *Small*, vol. 16, no. 15, pp. 1902827, 2020. DOI: 10.1002/smll.201902827.

- [5] A. N. Bashkatov, E. A. Genina, and V. V. Tuchin, "Optical properties of skin, subcutaneous, and muscle tissues: a review," *Journal of Innovative Optical Health Sciences*, vol. 4, no. 01, pp. 9-38, 2011. DOI: 10.1142/S1793545811001319

- [6] E. Moon, D. Blaauw, and J. D. Phillips, "Subcutaneous photovoltaic infrared energy harvesting for bio-implantable devices," *IEEE transactions on electron devices*, vol. 64, no. 5, pp. 2432-2437, 2017.

- Y.-J. Hung, H.-W. Su, C.-L. Chun, J.-F. Chen, C.-W. Huang, and M.-S. Cai, "Enhanced efficiency in backsideilluminated deep-n-well-assisted CMOS photovoltaic devices," *IEEE Electron Device Letters*, vol. 36, no. 11, pp. 1169-1171, 2015. DOI: 10.1109/LED.2015.2476380

- [8] Y.-J. Hung, M.-S. Cai, and H.-W. Su, "High-voltage generation in CMOS photovoltaic devices by localized substrate removal," *IEEE Electron Device Letters*, vol. 37, no. 6, pp. 754-757, 2016. DOI: 10.1109/LED.2016.2550496

- [9] F. Kaklin, J. Raynor, and R. Henderson, "High voltage generation using deep trench isolated photodiodes in a back side illuminated process." pp. 32.2. 1-32.2. 4. DOI: 10.1109/IEDM.2018.8614656.

- [10] M. Asscher, R. Sagi, C. Tamburu, O. Eli, I. C. Zamero, E. Pikhay, Y. Roizin, I. Lyubina, L. Bar-on, and A. Nahor, "Local isolation of high-voltage photovoltaic cells using buried layers of oxidized porous silicon," *IEEE Journal of Photovoltaics*, vol. 9, no. 4, pp. 992-997, 2019. DOI: 10.1109/JPHOTOV.2019.2912069

- B. Ciftcioglu, L. Zhang, J. Zhang, J. R. Marciante, J. Zuegel, R. Sobolewski, and H. Wu, "Integrated silicon PIN photodiodes using deep N-well in a standard 0.18-\$\mu \$ m CMOS technology," *Journal of lightwave technology*, vol. 27, no. 15, pp. 3303-3313, 2009. DOI: 10.1109/JLT.2008.2008664

- [12] M. K. Law, and A. Bermak, "High-voltage generation with stacked photodiodes in standard CMOS process," *IEEE Electron Device Letters*, vol. 31, no. 12, pp. 1425-1427, 2010. DOI: 10.1109/LED.2010.2075910

- [13] G. Hong, and G. Han, "Design optimization of photovoltaic cell stacking in a triple-well CMOS process," *IEEE Transactions on Electron Devices*, vol. 67, no. 6, pp. 2381-2385, 2020. DOI: 10.1109/TED.2020.2986536

- [14] Z. Chen, M.-K. Law, P.-I. Mak, and R. P. Martins, "A singlechip solar energy harvesting IC using integrated photodiodes for biomedical implant applications," *IEEE transactions on biomedical circuits and systems*, vol. 11, no. 1, pp. 44-53, 2016. DOI: 10.1109/TBCAS.2016.2553152

- [15] A. Technologies. "ABET Technology Sunlite Solar Simulators," 11/14, 2021; https://abettechnologies.com/solar-simulators/sunlite-solar-simulators/.

- [16] L. Lu, Z. Yang, K. Meacham, C. Cvetkovic, E. A. Corbin, A. Vázquez-Guardado, M. Xue, L. Yin, J. Boroumand, and G. Pakeltis, "Biodegradable monocrystalline silicon photovoltaic microcells as power supplies for transient biomedical implants," *Advanced Energy Materials*, vol. 8, no. 16, pp. 1703035, 2018.DOI: 10.1002/aenm.201703035

- [17] S. Ayazian, V. A. Akhavan, E. Soenen, and A. Hassibi, "A photovoltaic-driven and energy-autonomous CMOS implantable sensor," *IEEE Transactions on biomedical circuits and systems*, vol. 6, no. 4, pp. 336-343, 2012. DOI: 0.1109/TBCAS.2011.2179030

- [18] T. Tokuda, T. Ishizu, W. Nattakarn, M. Haruta, T. Noda, K. Sasagawa, M. Sawan, and J. Ohta, "1 mm3-sized optical neural stimulator based on CMOS integrated photovoltaic power receiver," *AIP advances*, vol. 8, no. 4, pp. 045018, 2018. DOI: 10.1063/1.5024243

- [19] A. Ahnood, K. Fox, N. Apollo, A. Lohrmann, D. J. Garrett, D. A. Nayagam, T. Karle, A. Stacey, K. M. Abberton, and W. A. Morrison, "Diamond encapsulated photovoltaics for transdermal power delivery," *Biosensors and Bioelectronics*, vol. 77, pp. 589-597, 2016. DOI: 10.1016/j.bios.2015.10.022

56

57

58 59 60