Kapoulea, S., Ahmad, M., Weides, M. and Heidari, H. (2023) Cryo-CMOS Mixed-Signal Circuits for Scalable Quantum Computing: Challenges and Future Steps. In: 2023 IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, CA, USA, 21-25 May 2023, ISBN 9781665451093.

Copyright © 2023 IEEE. Reproduced under a <u>Creative Commons Attribution 4.0</u> <u>International License</u>.

For the purpose of open access, the author(s) has applied a Creative Commons Attribution license to any Accepted Manuscript version arising.

https://eprints.gla.ac.uk/296426/

Deposited on: 13 April 2023

Enlighten – Research publications by members of the University of Glasgow <u>https://eprints.gla.ac.uk</u>

# Cryo-CMOS Mixed-Signal Circuits for Scalable Quantum Computing: Challenges and Future Steps

Stavroula Kapoulea, Meraj Ahmad, Martin Weides, and Hadi Heidari

James Watt School of Engineering, University of Glasgow

Glagsow G12 8QQ, UK

Email: {Stavroula.Kapoulea, Meraj.Ahmad, Martin.Weides, Hadi.Heidari}@glasgow.ac.uk

Abstract-A systematic research on the development of cryogenic complementary metal-oxide semiconductor (cryo-CMOS) circuits, for implementing the required control electronics to manipulate the quantum bit (qubit) state, is performed over the last few years. Scalability constitutes a key term regarding the evolution of quantum computing from theory to practical application and CMOS technology has been proven to be a promising candidate for implementing the coveted scalable next-generation quantum computers (QCs). Mixed-signal blocks, used for uniting the analog and digital domains, play a key role in the efficient functionality of the qubit control/readout system, thus there is an ever-increasing interest in their high-performance circuit realization. The critical challenge in this venture is to achieve efficient cryogenic operation at low temperatures, i.e., close to the qubit around 4 K, simultaneously keeping power requirements at low values. An overview and comparison of the cryo-CMOS Digital-to-Analog converter (DAC) and Analog-to-Digital converter (ADC) circuit implementations for quantum computing applications that heretofore have been proposed in the literature is presented in this work. A discussion on the challenges and future strategic steps that are henceforth required to proceed toward the development of a functional scalable quantum computer is also conducted.

Keywords—quantum computing, quantum control, cryogenic electronics, cryogenic CMOS circuits, mixed-signal circuits, analog-to-digital converters, digital-to-analog converters

#### I. INTRODUCTION

Interest in the practical implementation of future scalable quantum computers (QCs) has enriched the literature with a wealth of work on the challenges and potentials of designing complementary metal-oxide semiconductor (CMOS)-based circuits capable of operating at deep cryogenic temperatures [1-8]. The requirement for such circuits was generated from the necessity to gradually move the qubit control/readout unit from room temperatures (RT), and the restrictions of a bulky, delay-generating coupling between the quantum processor and the external environment, to lower temperatures closer to the qubits. The long-term objective of this method is to attain an integrated quantum computing System-on-Chip (SoC), which will comprise the quantum processor and the required control electronics at temperatures around 10 mK. Currently, such low-temperature operation is not practically feasible due to the limited cooling power of the available dilution refrigerators and the unavailability of reliable deep cryogenic device models. A provisional solution to overcome these drawbacks is to put the control/readout unit at the lowest possible temperature, i.e., around 4 K in close proximity to the

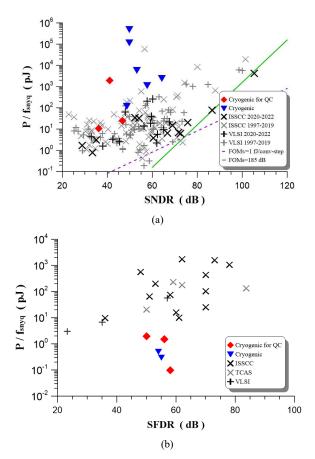

Fig. 1. Energy diagram for state-of-the-art (a) ADCs and (b) DACs. Blue triangle represents cryogenic ADCs/DACs, red rhombus cryogenic ADCs/DACs for quantum computing applications, whereas black and grey symbols correspond to room-temperature SAR ADS [14] and current-steering DACs.

qubits at 10 mK, in order to limit the high-speed interconnect to the external environment.

The efficacy of the qubit control/readout system relies heavily on two fundamental mixed-signal blocks, the Analogto-Digital converter (ADC) and Digital-to-Analog converter (DAC), thus significant research steps towards their cryogenic CMOS-based implementation have been taken in recent years [9–27]. A survey on the state-of-the-art literature for both types of converters is demonstrated in Fig. 1, highlighting the cryogenic and cryogenic quantum computing related works. More details for each type are provided in Sections II and III for ADCs and DACs, respectively.

This work was supported by the EPSRC EPIQC (EP/W032627/1), UKRI Innovate UK Cryo-CMOS to enable scalable quantum computers project (grant no. 10006017), and UKRI Innovate UK Altnaharra: Cryoelectronics for Quantum Circuits project (grant no. 10006186).

As expected, there are important variations in the performance characteristics of solid-state electronics at such low temperatures compared to the conventional roomtemperature performance. Hence, the main obstacle in the cryo-CMOS circuit design process is the unavailability of cryogenic MOS transistor models that would directly achieve an efficient operation of the circuit at the desired low temperature. Characterization of the current transistor models of different nanoscale technologies at cryogenic temperatures has shown that the most critical performance features are importantly affected while approaching values of liquid Helium temperature and lower, i.e., increase in threshold voltage, charge mobility and transistor mismatch, a fact that demonstrates the emerging need for generating accurate cryo-CMOS models [27-35]. Exploiting the results obtained by the characterization process, the currently available roomtemperature models have been used as a tentative solution for building cryogenic circuitry for quantum computing purposes.

The paper is structured as follows: Section II summarizes the steps taken up to this point to implement a cryo-CMOS ADC, whereas Section III provides the corresponding information about its inverse counterpart, i.e., a cryo-CMOS DAC. Concluding, existing challenges in the field and future directions towards the development of progressively more advanced cryogenic quantum circuits are discussed in Section IV.

# II. ANALOG-TO-DIGITAL CONVERTERS

#### A. Architecture Techniques

Quantum readout operations require fast sampling rates (~GHz), wide bandwidth (~MHz–GHz), and low power consumption (~mW). Though, reading the state of one qubit requires a few tens of MHz sampling frequency, so why to use such a higher speed after all? The answer is: scalability! Combining the individual qubit signals utilizing the frequency-division multiplexing (FDM) technique, the required circuitry for their digitalization can be considerably simplified, allowing the simultaneous readout of multiple qubits, and reducing the power requirements of the system. To make this point clear, let us consider a sampling rate ( $f_s$ ) of 2 GHz and a qubit frequency of 20 MHz. The efficient bandwidth will be approximately  $f_s/2=1$  GHz, which means that the readout of ~50 qubits is attainable.

ADCs constitute fundamental building blocks of the frequency-multiplexed qubit readout process, down sampling the (amplified) analog I/Q signals to "read" the qubit state. Among the commonly used ADC architectures are the direct-conversion (or flash), the conventional successive-approximation register (SAR), and enhanced versions of SAR to achieve even higher speed. The main building block of all these architectures is the comparator, which along with a sample-and-hold circuit turns the continuous input signal into digital bits. SAR ADCs also use internal DACs, commonly formed by charge-scaling capacitive structures (CDACs), avoiding resistive reference ladders.

Even though flash architecture provides a simultaneous high-speed conversion, its performance in terms of power and efficient resolution at higher sampling rates makes it a nonideal option for quantum computing applications [9]. On the other hand, SAR architecture has been proven to be a suitable candidate, due to its robustness against the effects caused by temperature fluctuations and its high energy efficiency. A critical part of the SAR ADC's functionality is the

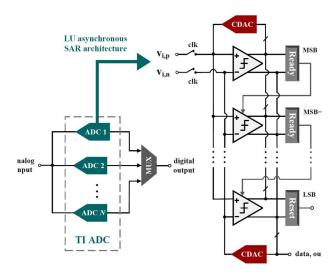

Fig. 2. Time-interleaved (TI) loop-unrolled (LU) successiveapproximation register (SAR) ADC architecture.

synchronization of its individual blocks' operations. The asynchronous operation, demonstrated in functional block diagram form in Fig. 2, can offer around 50% higher sampling rate than the synchronous one at the cost of a more complicated structure [15]. The key point in this architecture is the substitution of the sequential bit decision for the parallel execution of the SAR operations, thus reducing the time required for a complete comparison cycle, which becomes equal to the sum of the comparator decision time and the DAC settling time. An important feature of this configuration is that the additional comparator stages do not considerably affect the total power requirement, as each stage is activated once per cycle.

Enhanced performance of the asynchronous SAR ADC, to meet the quantum computing requirements in terms of speed and power, can be achieved by exploiting two techniques: loop unrolling and time-interleaving sampling. Applying the loop-unrolling method, the obtained data are directly stored at the comparator, thus reducing the required iterations for decision, and simplifying the digital logic stage. Considering that the desired sampling rate is in the order of GHz, an impractical resolution reduction is required to reach such high values of speed. To maintain the desired resolution and simultaneously achieve GHz-level of sampling rate, timeinterleaved (TI) loop-unrolled (LU) asynchronous SAR ADC architecture can be utilized, achieving an ideal trade-off between resolution and speed [11,12].

# B. Cryogenic CMOS-based ADCs

A comprehensive guide regarding the ADC publications in the literature over the past 25 years is provided by Murmann's ADC overview table, which is available online [14]. A review of this table and the rest of the literature shows that although cryogenic ADC designs have already been proposed over the past decade, only in the last two years have detailed works been published on cryo-CMOS ADC design for quantum computing applications [10–12]. The energy diagram in Fig. 1(a) provides a clear picture of the state-ofthe-art room-temperature (black/grey symbols), cryogenic (blue tringles) and cryogenic for quantum computing applications (red rhombus) ADCs over the past 25 years.

| Parameter                    | Value                |                      |                         |           |  |  |

|------------------------------|----------------------|----------------------|-------------------------|-----------|--|--|

| rarameter                    | [12]                 |                      | [11]                    | [10]      |  |  |

| Temperature (K)              | 300                  | 4.2                  | 4.2                     | 3         |  |  |

| Technology (nm)              | 40 CMOS              |                      | 40 CMOS                 | 22 FinFET |  |  |

| Architecture                 | TI-LU-SAR            |                      | TI-LU-SAR               | SAR       |  |  |

| Resolution (bit)             | 7                    |                      | 6-8                     | N/A       |  |  |

| ENOB (bit)                   | 6.5                  |                      | 5.7                     | 7.5       |  |  |

| Sampling rate<br>(MS/s)      | 1000                 |                      | 1000                    | 400       |  |  |

| Area (mm <sup>2</sup> )      | 0.042ª               |                      | 0.045ª                  | N/A       |  |  |

| Supply (V)                   | 1.1                  |                      | 1.1 (core)<br>2.5 (clk) | N/A       |  |  |

| Input range (Vpp)            | 0.6                  |                      | 0.7                     | N/A       |  |  |

| DNL (LSB)                    | <0.55                |                      | <1.5                    | N/A       |  |  |

| INL (LSB)                    | <0.55                |                      | <1.2                    | N/A       |  |  |

| SNDR@Nyquist<br>(dB)         | 38.2                 | 41.1                 | 36.2                    | 46.8      |  |  |

| SFDR (dB)                    | >50 <sup>b</sup>     |                      | 48.5                    | N/A       |  |  |

| FoM <sub>w</sub> (fJ/c.step) | 29.2 <sup>a, b</sup> | 20.9 <sup>a, b</sup> | 200 <sup>a, b</sup>     | N/A       |  |  |

| Power (mW)                   | 1.94ª                |                      | 10.6ª                   | 38°       |  |  |

<sup>a.</sup> ADC core + clock receiver, <sup>b.</sup> Typical sample, <sup>c.</sup> Total receiver

One of the first attempts to bring ADCs closer to the qubit temperature was based on a Xilinx Artix 7 FPGA cooled down to 15 K [13]. Despite the full programmability and low cost, the critical parameters' variation caused by the cryogenic-temperature environment, and the increased power consumption (850 mW for the whole system) render this option impractical for implementing scalable quantum computers. The situation is quite the opposite in the case of cryogenic ADCs based on nanoscale integrated circuits, where the typical power dissipation is less than 1 mW in most cases [10–12].

To perform a fair comparison, but also demonstrate the variations between different architectures, the roomtemperature and cryogenic performance characteristics of the most recently published TI LU-SAR ADC in [12] are tabulated along with the corresponding cryogenic ones presented in [10] and [11], and the results are summarized in Table I. Comparing the work in [10] with the one in [12], the sampling rate, a critical feature for achieving scalability, tremendously increases (×2 times) in the case of TI LU-SAR ADC compared to the SAR ADC with the efficient number of bits (ENOB) being slightly decreased. Impressive is also the power reduction that the authors achieved in [12] compared to their work in [11], utilizing a latching comparator optimized for cryogenic temperatures. This demonstrates the critical role of the comparator in the ADC performance, guiding the future research directions towards the further optimization of this fundamental block.

#### **III. DIGITAL-TO-ANALOG CONVERTERS**

# A. Architecture Techniques

DACs are utilized in both qubit control and readout operations, and for implementing SAR ADCs as mentioned in the previous Section, transforming the digitized signals to the

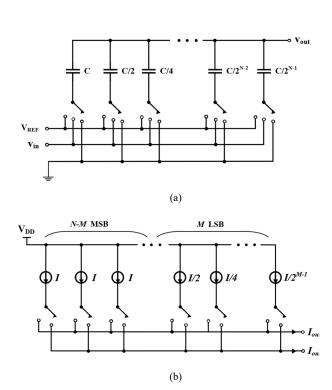

Fig. 3. DAC architectures: (a) capacitive (CDAC), and (b) segmented current steering (CS). *N* indicates the number of bits.

real-world analog domain. DACs have garnered great research interest, which is reflected in the number of related publications in the literature [16-28]. Depending on the type of qubit, DC/Bias, Pulse and/or Intermediate Frequency (IF) signal DACs may be required for generating the bias DC voltages that form the qubit potential wells, gate pulse voltage and IF frequency after up modulation to perform qubit gate operations, respectively. Gate pulsing has only been discussed in [10], where a complete system-on-chip is presented, including the control and readout of a 7-qubit processor, focusing on a system level and not specifically on the DAC operation. The main difference between bias and IF-signal DACs is the required sampling rate. In the first case, it is around the qubit frequency, i.e., in the order of MHz, whereas in the second case high sampling rates in the order of GHz are required, due to the multiple IF frequencies that an up-scaled quantum control circuitry demands.

Three typical configurations used to construct a DAC are: (i) resistive-ladder, (ii) capacitive, or charge-redistribution (CDAC) and (iii) current-steering (CS) DACs. Resistive DAC is inappropriate for high-speed applications, due to the large area requirements and the low power efficiency. On the other hand, capacitive, also known as charge-redistribution, DACs constitute a fair solution, due to the advantages of high-speed operation and low power consumption. As demonstrated in Fig. 3(a), their structure is based on wellmatched capacitances, whose terminal connections are adjusted through digitally controlled switches. The main advantages of this configuration, regarding its cryogenic temperature performance, are the decreased total thermal noise power of the signal (kT/C) and the limited effect on CMOS transistors, when operating as transmission gates or digital control logic [16]. The last type, and most promising

for GHz-frequency qubit control operations, is the currentsteering DAC shown in Fig. 3(b).

Among the advantages of the current-steering structure, that make it appropriate for quantum computing applications, are high speed (much higher than the other two types), differential signal operation, and better linearity [36]. In addition, in many cases, even at high sampling rates, there is no requirement for an output buffer stage, thus reducing the circuit complexity. The unit element of the current-steering DAC can be arranged in both binary and unary-weighted, also known as thermometer-decoded, fashion. However, to get the best of both types, segmented CS DACs, i.e., a combination of binary and unary-weighted structures, are preferred in most cases to achieve trade-off between monotonicity and area/routing challenges. The main drawback of both chargeredistribution and current-steering DACs, which should always be carefully considered, is the capacitor and current source mismatches, respectively, caused by the cryogenic temperature environment. This is also the main source for nonlinearity effects.

# B. Cryogenic CMOS-based DACs

Current-steering architecture has proven to be an ideal candidate in all types of DACs, thus dominates in the literature. A preliminary state-of-the-art survey is demonstrated in Fig. 1(b), including cryogenic CS DACs for quantum computing (red rhombus) and for other applications (blue tringles), along with the most cited room-temperature CS DAC publications (black/grey symbols) over the past 20 years.

For comparison purposes, four of the most recent and complete works of this survey are presented in Table II [19,21,24,27]. As it is expected, the requirement for higher sampling rate induces higher resolution and power demand. For cryogenic DACs used for generating solid-state qubit bias voltages and sample at a speed of MS/s, 8-bit resolution is an efficient option, while the power consumption for these specifications is in the order of some  $\mu$ W [19,27]. DACs used for IF signal generation purposes, where the speed is greater than 1 GS/s, 10-bit resolution is a typical choice, whereas the consumed power is about some mW [21,24]. Another important characteristic in this case is the spurious-free dynamic range (SFDR), whose value should exceed the limit of 45 to achieve IF frequency >1 GHz.

The following points should be considered, when evaluating the performance of a DAC through the characteristics tabulated above. Resolution is a critical feature for the signal conversion that should be up to 8 bits to ensure a high-fidelity drive of the qubit state [16]. Power consumption also depends on the utilized CMOS technology, thus, even though the specifications in [19] and [27] are of similar values, the power required in [27], where 40-nm technology is used, is almost double than the power consumed in [19], where the DAC circuitry is built using 28-nm technology. As long as the sampling rate concerned, the higher it is, the greater the number of the manipulated qubits are, and this is the objective for attaining large-scale quantum computing systems. The critical point is to achieve a good balance between all these characteristics, while simultaneously ensuring an efficient DAC performance, and current-steering architecture has proven to be the best choice.

| TABLE II. | CRYOGENIC DAC PERFORMANCE COMPARISON |

|-----------|--------------------------------------|

|-----------|--------------------------------------|

| <b>D</b> (              | Value        |                |            |             |  |

|-------------------------|--------------|----------------|------------|-------------|--|

| Parameter               | [24]         | [21]           | [27]       | [19]        |  |

| Temperature (K)         | 3            | 3              | 10         | 4.2         |  |

| Function                | IF signal    | IF signal      | Bias       | Bias        |  |

| Technology (nm)         | 14<br>FinFET | 22<br>FinFET   | 40<br>CMOS | 28<br>FDSOI |  |

| Architecture            | CS           | CS             | CS         | CS          |  |

| Resolution (bits)       | 10           | 10             | 8          | 8           |  |

| Sampling rate<br>(GS/s) | 1            | 2.5            | 0.14       | 0.1         |  |

| Area (mm <sup>2</sup> ) | 1.61ª        | 4 <sup>b</sup> | 0.0074ª    | 0.04ª       |  |

| Output range (mV)       | N/A          | N/A            | 6          | 6.6         |  |

| DNL (LSB)               | N/A          | 2              | 0.18       | 0.64        |  |

| INL (LSB)               | N/A          | 0.5            | 0.61       | 2.96        |  |

| SFDR (dB)               | 50           | 56             | 58         | N/A         |  |

| Power (mW)              | 1.92ª        | 1.5ª           | 0.0138ª    | 0.0073ª     |  |

<sup>a.</sup> DAC core, <sup>b.</sup> Total TX

### IV. DISCUSSION

Control electronics for the state manipulation and readout of an upscaled number of physical qubits should meet two main requirements: (i) high speed, and (ii) low power consumption. No access to cryogenic electronic device models and dilution refrigerators of limited cooling power are at the core of the insurmountable scalability problem in the development of quantum computers. To accomplish this goal, the establishment of well-founded cryogenic transistor and passive components' models, based on contemporary advanced nanoscale CMOS technologies, is urgently needed. Nevertheless, exploiting the tools available at this point to set the foundations in the development of qubit control electronics is dominant to enable large-scale quantum computers in the future. Speed and robustness enhancement against the variations of the CMOS device characteristics, when cooled down at cryogenic temperatures, is required at this intermediate research stage. Based on that, future steps should focus on more stable structures and calibration techniques to efficiently eliminate the effects of sub-Kelvin temperatures on the CMOS circuitry until appropriate models are developed.

The up-to-date literature on the chief mixed-signal building blocks, i.e., ADCs and DACs, presented in this work demonstrates the great interest in this field and the significant leaps that have been achieved up to the present. Academic and industrial research worlds have joined forces to shape the future of quantum computing. Among the pioneers of the next-generation data revolution are names of big companies and universities around the world, like IBM, Google, Rigetti, Quantum Motion, University of Waterloo, MIT, Harvard University, University of Oxford, TU Delft and recently the University of Glasgow. The collaboration between leading groups in the field and the development of a protocol will define a common path for the quantum computing community and accelerate the evolution of scalable quantum computers.

# REFERENCES

- E. Charbon, et al., "Cryo-CMOS circuits and systems for scalable quantum computing," 2017 IEEE International Solid-State Circuits Conference (ISSCC), 2017, pp. 264-265.

- [2] B. Patra, et al., "Cryo-CMOS Circuits and Systems for Quantum Computing Applications," in *IEEE Journal of Solid-State Circuits*, vol. 53, no. 1, pp. 309-321, Jan. 2018.

- [3] J. C. Bardin, et al., "Design and Characterization of a 28-nm Bulk-CMOS Cryogenic Quantum Controller Dissipating Less Than 2 mW at 3 K," in *IEEE Journal of Solid-State Circuits*, vol. 54, no. 11, pp. 3043-3060, Nov. 2019

- [4] J. van Dijk, et al., "Cryo-CMOS for Analog/Mixed-Signal Circuits and Systems," 2020 IEEE Custom Integrated Circuits Conference (CICC), 2020, pp. 1-8.

- [5] S. Pellerano, et al., "Cryogenic CMOS for Qubit Control and Readout," 2022 IEEE Custom Integrated Circuits Conference (CICC), 2022, pp. 01-08.

- [6] R. B. Staszewski, I. Bashir, E. Blokhina and D. Leipold, "Cryo-CMOS for Quantum System On-Chip Integration: Quantum Computing as the Development Driver," *in IEEE Solid-State Circuits Magazine*, vol. 13, no. 2, pp. 46-53, Spring 2021.

- [7] E. Charbon, "Cryo-CMOS Electronics For Quantum Computing: Bringing Classical Electronics Closer To Qubits In Space And Temperature," in *IEEE Solid-State Circuits Magazine*, vol. 13, no. 2, pp. 54-68, Spring 2021.

- [8] M. Ahmad, C. Giagkoulovits, S. Danilin, M. Weides, and H. Heidari, "Scalable Cryoelectronics for Superconducting Qubit Control and Readout." *Advanced Intelligent Systems* (2022): 2200079.

- [9] Y. Creten, P. Merken, W. Sansen, R. P. Mertens and C. Van Hoof, "An 8-Bit Flash Analog-to-Digital Converter in Standard CMOS Technology Functional From 4.2 K to 300 K," in *IEEE Journal of Solid-State Circuits*, vol. 44, no. 7, pp. 2019-2025, July 2009.

- [10] J. Park et al., "A Fully Integrated Cryo-CMOS SoC for State Manipulation, Readout, and High-Speed Gate Pulsing of Spin Qubits," in *IEEE Journal of Solid-State Circuits*, vol. 56, no. 11, pp. 3289-3306, Nov. 2021.

- [11] G. Kiene, et al., "13.4 A 1GS/s 6-to-8b 0.5mW/Qubit Cryo-CMOS SAR ADC for Quantum Computing in 40nm CMOS," 2021 IEEE International Solid-State Circuits Conference (ISSCC), 2021, pp. 214-216.

- [12] G. Kiene, A. G. Sreenivasulu, R. W. J. Overwater, M. Babaie and F. Sebastiano, "Cryogenic Comparator Characterization and Modeling for a Cryo-CMOS 7b 1-GSa/s SAR ADC," ESSCIRC 2022- IEEE 48th European Solid State Circuits Conference (ESSCIRC), 2022, pp. 53-56.

- [13] H. Homulle, S. Visser and E. Charbon, "A Cryogenic 1 GSa/s, Soft-Core FPGA ADC for Quantum Computing Applications," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 63, no. 11, pp. 1854-1865, Nov. 2016.

- [14] B. Murmann, "ADC Performance Survey 1997-2022," [Online]. Available: <u>http://web.stanford.edu/~murmann/adcsurvey.html</u>

- [15] T. Jiang, W. Liu, F. Y. Zhong, C. Zhong, K. Hu and P. Y. Chiang, "A Single-Channel, 1.25-GS/s, 6-bit, 6.08-mW Asynchronous Successive-Approximation ADC With Improved Feedback Delay in 40-nm CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 47, no. 10, pp. 2444-2453, Oct. 2012.

- [16] C. Degenhardt et al., "Systems Engineering of Cryogenic CMOS Electronics for Scalable Quantum Computers," 2019 IEEE International Symposium on Circuits and Systems (ISCAS), 2019, pp. 1-5.

- [17] J. C. Bardin et al., "29.1 A 28nm Bulk-CMOS 4-to-8GHz <2mW Cryogenic Pulse Modulator for Scalable Quantum Computing," 2019 IEEE International Solid- State Circuits Conference (ISSCC), 2019, pp. 456-458.

- [18] A. Esmailiyan et al., "A Fully Integrated DAC for CMOS Position-Based Charge Qubits with Single-Electron Detector Loopback

Testing," in IEEE Solid-State Circuits Letters, vol. 3, pp. 354-357, 2020.

- [19] M. E. P. V. Zurita et al., "Cryogenic Current Steering DAC With Mitigated Variability," in *IEEE Solid-State Circuits Letters*, vol. 3, pp. 254-257, 2020.

- [20] J. P. G. Van Dijk et al., "A Scalable Cryo-CMOS Controller for the Wideband Frequency-Multiplexed Control of Spin Qubits and Transmons," in *IEEE Journal of Solid-State Circuits*, vol. 55, no. 11, pp. 2930-2946, Nov. 2020.

- [21] B. Patra et al., "19.1 A Scalable Cryo-CMOS 2-to-20GHz Digitally Intensive Controller for 4×32 Frequency Multiplexed Spin Qubits/Transmons in 22nm FinFET Technology for Quantum Computers," 2020 IEEE International Solid-State Circuits Conference (ISSCC), 2020, pp. 304-306.

- [22] K. Kang et al., "A 5.5mW/Channel 2-to-7 GHz Frequency Synthesizable Qubit-Controlling Cryogenic Pulse Modulator for Scalable Quantum Computers," 2021 Symposium on VLSI Circuits, 2021, pp. 1-2.

- [23] D. J. Frank et al., "22.1 A Cryo-CMOS Low-Power Semi-Autonomous Qubit State Controller in 14nm FinFET Technology," 2022 IEEE International Solid-State Circuits Conference (ISSCC), 2022, pp. 360-362.

- [24] S. Chakraborty et al., "A Cryo-CMOS Low-Power Semi-Autonomous Transmon Qubit State Controller in 14-nm FinFET Technology," in *IEEE Journal of Solid-State Circuits*, vol. 57, no. 11, pp. 3258-3273, Nov. 2022.

- [25] K. Kang et al., "A Cryo-CMOS Controller IC With Fully Integrated Frequency Generators for Superconducting Qubits," 2022 IEEE International Solid-State Circuits Conference (ISSCC), 2022, pp. 362-364.

- [26] K. Kang et al., "A 40-nm Cryo-CMOS Quantum Controller IC for Superconducting Qubit," in *IEEE Journal of Solid-State Circuits*, vol. 57, no. 11, pp. 3274-3287, Nov. 2022.

- [27] Y. Hu et al., "Cryo-CMOS Model-Enabled 8-Bit Current Steering DAC Design for Quantum Computing," 2022 IEEE International Symposium on Circuits and Systems (ISCAS), 2022, pp. 3413-3417.

- [28] R. M. Incandela, L. Song, H. Homulle, E. Charbon, A. Vladimirescu and F. Sebastiano, "Characterization and Compact Modeling of Nanometer CMOS Transistors at Deep-Cryogenic Temperatures," in *IEEE Journal of the Electron Devices Society*, vol. 6, pp. 996-1006, 2018.

- [29] P. A. 't Hart, J. P. G. van Dijk, M. Babaie, E. Charbon, A. Vladimircscu and F. Sebastiano, "Characterization and Model Validation of Mismatch in Nanometer CMOS at Cryogenic Temperatures," 2018 48th European Solid-State Device Research Conference (ESSDERC), 2018, pp. 246-249.

- [30] S. Bonen et al., "Cryogenic Characterization of 22-nm FDSOI CMOS Technology for Quantum Computing ICs," in *IEEE Electron Device Letters*, vol. 40, no. 1, pp. 127-130, Jan. 2019

- [31] Beckers, Arnout, et al., "Characterization and modeling of 28-nm FDSOI CMOS technology down to cryogenic temperatures," *Solid-State Electronics*, 159 (2019): 106-115.

- [32] F. Imroze, et al., "Packaged CMOS cryogenic characterization for quantum computing applications," 29th IEEE International Conference on Electronics Circuits and Systems (ICECS), 2022, in press.

- [33] D. Andrade-Miceli, et al., "Characterisation and Modelling of 22-nm FD-SOI Transistors Operating at Cryogenic Temperatures," 29th IEEE International Conference on Electronics Circuits and Systems (ICECS), 2022, in press.

- [34] C. Giagkoulovits, et al., "CryoCMOS Characterization Strategies and Challenges," 29<sup>th</sup> IEEE International Conference on Electronics Circuits and Systems (ICECS), 2022, in press.

- [35] Bonen, Shai, et al., "Harnessing the Unique Features of FDSOI CMOS Technology in Fibreoptic, Millimetre-Wave, and Quantum Computing Circuits From 2 K to 400 K," *Solid-State Electronics* (2022): 108343.

- [36] B. Razavi, "The Current-Steering DAC [A Circuit for All Seasons]," in *IEEE Solid-State Circuits Magazine*, vol. 10, no. 1, pp. 11-15, Winter 2018.