Guan, Y., Georgiev, V. P., Asenov, A., Liang, F. and Chen, H. (2022) Impact of the Figures of Merit (FoMs) definitions on the variability in nanowire TFET: NEGF simulation study. IEEE Transactions on Electron Devices, 69(11), pp. 6394-6399.

Copyright © 2022 IEEE. Reproduced under a <u>Creative Commons Attribution 4.0</u> <u>International License</u>.

For the purpose of open access, the author(s) has applied a Creative Commons Attribution license to any Accepted Manuscript version arising.

https://eprints.gla.ac.uk/278369/

Deposited on: 2 September 2022

Enlighten – Research publications by members of the University of Glasgow https://eprints.gla.ac.uk

# Impact of the Figures of Merit (FoM) Definitions on the Variability in Nanowire TFET: NEGF Simulation Study

Yunhe Guan, Vihar P. Georgiev, *Senior Member*, *IEEE*, Asen Asenov, *Fellow*, *IEEE*, Feng Liang, and Haifeng Chen

Abstract-In this paper we investigate the effect of variability in p-type nanowire Tunnel FET (TFET) using quantum mechanical transport simulations. The simulations have been carried out using the Nano Electronics Simulation Software (NESS) from the University of Glasgow. Random discrete dopants and work-function variations have been investigated in the simulations. Our statistical simulations reveal that key Figures of Merit (FoM) such as the current variability generally decreases as the gate voltage decreases, the threshold voltage variability increases as the threshold current increases, and the dependences of these FoM variabilities on criteria become stronger with the switch characteristic ameliorated. Furthermore, it is interesting to find that the band-offset in heterostructure can more or less alleviate the current variability, especially around the off-state.

*Index Terms*—Criteria of Figures of Merit, Nanowire Tunnel FET, Quantum simulation, Random discrete dopants (RDD), Variability, Work-function variations (WFV).

# I. INTRODUCTION

Tunnel FETs (TFETs) are being considered as a promising candidate for low power applications in future technology nodes due to their capability to overcome the thermionic subthreshold slope limitation delivering sub-60mV/decade sunthreshold swing (SS) [1]. It has been shown that the diameter of III-V nanowires can be reduced down to a few nanometers [2], as reported by Lund university reaching 7 nm

This work was supported in part by the National Natural Science Foundation of China under Grants 61474093 and 62104192, Natural Science Basic Research Program of Shaanxi Province under Grant 2020JM-581 and Grant 2021JQ-717. This project has also received funding from EPSRC UKRI Innovation Fellowship scheme under grant agreement No. EP/S001131/1 (QSEE) and EPSRC UKRI with grant agreement No. EP/P009972/1 (QUANTDEVMOD) (Corresponding author: Yunhe Guan.)

Y. Guan and H. Chen are with the School of Electronic Engineering, Xi'an University of Posts & Telecommunications, Xi'an 710121, Shaanxi, P. R. China (e-mail: <u>gyhflc@xupt.edu.cn</u>).

V. P. Georgiev and A. Asenov are with the James Watt School of Engineering, University of Glasgow, Glasgow G12 8LT, U.K.

F. Liang is with the School of Microelectronics, Xi'an Jiaotong University, Xi'an 710049, Shaanxi, P. R. China.

in III-V TFET by using digital etching technique [3]. For these truly nanometric size devices, dominated by the quantum mechanical effects, the performance variabilities induced by the discreteness of charge and granularity of matter have emerged as crucial concerns for their integration in billions of transistors count chips [4]-[6].

The previous studies covering the variability aspect in TFET, mainly focus on statistical variations of the Figures of Merit (FoM) which are defined by some fixed criteria [5]-[9]. Opposite to MOSFETs, the TFETs have SS that are no longer linear on a logarithmic scale [1], meaning that the FoM criteria should have influence on the variability. However, the impact of the definition of the FoM on the variability is missing from previous reports. This obscures the variability issue in TFETs when operating under different biasing conditions and the device optimization in terms of statistical variability and reliability.

In this paper, using quantum simulations, we have studied the correlation between the definition criteria and the statistical variations of the main FoM in p-type nanowire TFETs under the influences of random discrete dopants (RDD) and work-function variations (WFV). This paper is organized as follows. In Section 2, the device design and the simulation methodology are described. In Section 3, the dependence of drain current ( $I_{ds}$ ) and threshold voltage ( $V_{th}$ ) variations on the gate bias and threshold current criteria, are respectively analyzed under different source doping, structure, and metal-grain size. Finally, the conclusions are drawn in Section 4.

### II. DEVICE DESCRIPTION AND METHODOLOGY

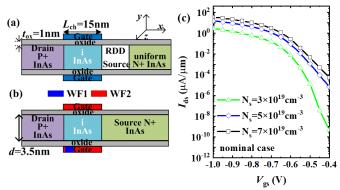

The p-type InAs nanowire TFETs considered in this work under the influence of RDD and WFV are illustrated in Fig. 1(a) and (b) respectively. The surface roughness (SR) is not considered here due to that it presents less variability as presented in our previous work [10], [11]. Whereas, the SR shows relatively obvious impact on nanowire TFET in Ref. [12]. The different observations can be attributed to the difference of device type adopted. The device in our work is p-type, and in Ref. [12] it is n-type. It should be noted that the channel subband fluctuations are responsible for the impact of SR, since source subband appears relatively smoother due to

Fig. 1. Sketch of a nanowire InAs TFET with (a) RDD and (b) WFV configurations. (c) Nominal  $I_{ds} - V_{gs}$  characteristics under various source dopings.  $L_{ch} = 15$ nm, d = 3.5nm,  $t_{ox} = 1$ nm, and  $V_{ds} = -0.5$ V.

the macroscopic band bending [12]. Thus, for p-type (n-type) device, it is channel valence (conduction) subband which has a relatively larger (smaller) effective mass that plays a primary role in terms of variability, thus the impact of quantum confinement by SR is small (large). The simulated nanowire diameter is d = 3.5nm, the channel length is  $L_{ch} = 15$ nm, and the high-k oxide thickness is  $t_{ox} = 1$ nm with a relative dielectric constant  $\varepsilon = 9$ . The acceptor-type drain region is doped with  $N_d = 5 \times 10^{19}$  cm<sup>-3</sup>. The values of the effective mass in Ref. [11] are adopted for confined InAs materials. The channel is intrinsic and the doping profiles are assumed to be abrupt between the reservoirs and the channel. The drain-to-source voltage  $V_{ds}$  is set to -0.5V, unless otherwise specified. Fig. 1(c) shows the nominal  $I_{ds} - V_{gs}$  characteristics under various donor-type source doping  $N_s$ .

Details on the generation of nanowires with random RDD and WFV configurations can be found in Refs. [11] and [7], respectively. The RDD region is 10 nm long, as shown in Fig. 1(a), preceded by a uniform doped region required for numerical stability. The WFV-induced variability is introduced by the random grain orientations found in the TiN gate-all-around contact, as shown in Fig. 1(b) [13]. As like in Refs. [14] and [5] with nanowire structure, the TiN metal with two distinct grain orientations, which are set with 60% and 40% occurring probability and meaningful work-function difference of 0.2 eV [15], has been adopted. However, the selected work function values are not always consistent [5], [14]. They are respectively set as 5.3 eV and 5.1 eV for convergence purpose here. Although the choice of work function value or probability distribution will change the variability, the variation trends of variability will not be influenced. For example, the envelopes of variability are same when comparing the cases with two different groups of work function values [16]. The objective of this paper is to provide the dependence of variability on the bias or current criteria, and this is a trend analysis as like in Refs. [14] and [5]. Thus, we believe the work-function values or probability distributions have no influence on our conclusion. The default value of the average metal grain size is set to 3 nm. Simulations are carried out by employing the quantum transport module in NESS [11], [17], [18]. In order to accurately compute the band-to-band tunneling current in the ultra-scaled nanowire, the two-band Flietner model of the imaginary dispersion is used in combination with the couple

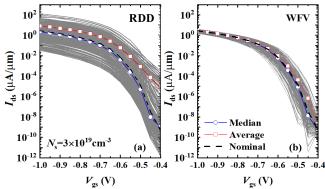

Fig. 2. The individual influence of (a) RDD and (b) WFV on the  $I_{ds} - V_{gs}$  characteristics of an ensemble of 200 nanowire TFETs. The nominal, median and average data are also shown.  $N_s = 3 \times 10^{19} \text{ cm}^{-3}$ .

mode-space NEGF approach [17]. The electron-phonon interactions are neglected since the tunneling in the studied devices is mainly direct, as reported in Ref. [11]. The accuracy of results from NESS has been previously verified by comparing with that from the atomistic tool OMEN [17]. In these extreme narrow nanowires, the majority of the electrons/holes are located in the lowest/highest conduction/valence subbands. Then, changing the number of conduction/valence subbands from 4, 8 up to 12 did not bring any additional novelties on our findings. For sake of saving on computational time, the simulations presented in this paper were carried out with 4 subbands for each carrier valley.

## **III. RESULTS AND DISCUSSIONS**

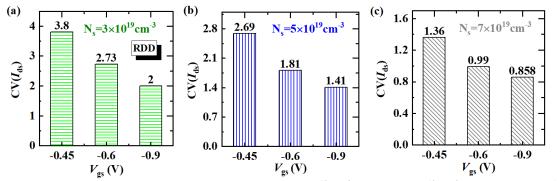

In order to carry out a reliable statistical analysis of variability introduced by RDD and WFV, ensembles of 200 nanowire TFETs have been simulated for various  $N_s$  first. As an example, Figs. 2(a) and 2(b) show the  $I_{ds} - V_{gs}$ characteristics of each of the 200 TFETs subject to the RDD and WFV variability for  $N_s = 3 \times 10^{19} \text{ cm}^{-3}$ , respectively. The nominal, average and median characteristics are also shown. It can be found that RDD has stronger impact on the variability of the  $I_{ds} - V_{gs}$  characteristics in comparison to WFV. In order to analyze the effect of OFF/ON-bias criteria, the dependences of the  $I_{ds}$  variation induced by RDD on the gate voltage under various  $N_s$  is presented in Fig. 3. It should be noted that the coefficient of variation (CV), defined as normalized deviation  $\sigma/\mu$ , is used to quantify the performance difference under different parameters, as adopted in Ref. [19].  $\sigma$ and  $\mu$  are the standard deviation and mean value of the corresponding FoM. From Fig. 3, it can be found that  $CV(I_{ds})$ generally decreases with the decrease of  $V_{gs}$  for each  $N_s$ . For example,  $CV(I_{ds})$  is 2.23, 1.46, and 1.18 at  $V_{gs} = -0.45V$ , -0.6V, and -0.9V under  $N_s = 5 \times 10^{19} \text{ cm}^{-3}$ , which means that the current around the OFF-state are more susceptible to the variability than those around the On-state. This indeed is consistent with the current distribution in Fig. 2. When TFET is biased around its ON/OFF-state, the electrical field near the tunneling junction is high/small, and the power law/exponential dependence of transmission on the electrical filed dominates the current [20]. As a result, the influence of the electrical field fluctuation resulted from RDD and thus the variation of current around the ON/OFF-state is relatively weaker/stronger.

Fig. 3. Dependences of normalized current variation by RDD on  $V_{gs}$  under (a)  $N_s = 3 \times 10^{19} \text{cm}^{-3}$ , (b)  $N_s = 5 \times 10^{19} \text{cm}^{-3}$ , and (c)  $N_s = 7 \times 10^{19} \text{cm}^{-3}$  in InAs TFET.

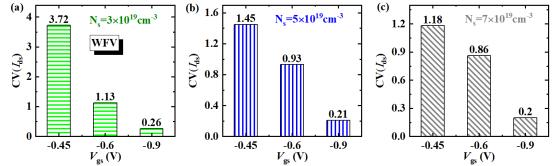

Fig. 4. Dependences of normalized current variation by WFV on  $V_{gs}$  under (a)  $N_s = 3 \times 10^{19} \text{cm}^{-3}$ , (b)  $N_s = 5 \times 10^{19} \text{cm}^{-3}$ , and (c)  $N_s = 7 \times 10^{19} \text{cm}^{-3}$  in InAs TFET.

Fig. 4 shows the dependences of the normalized variability of  $I_{ds}$  due to WFV on the gate voltage under various  $N_s$ . The same tendency is observed as in Fig. 3, with the relative variability becoming weak as  $V_{gs}$  decreases. This can also be explained by our analyses above. Comparing the quantitative data in Figs. 3 and 4, the CV( $I_{ds}$ ) at -0.9V of  $V_{gs}$  under WFV influence is around 0.2, much smaller than the variability under RDD influence. It reveals clearly that the current at lower  $V_{gs}$  is less affected by WFV compared to RDD.

From both of Figs. 3 and 4, it can be found that higher source doping reduces the current variations in InAs TFET. At  $V_{gs} = -0.6V$ ,  $CV(I_{ds})$  induced by RDD (WFV) decreases from 2.73 (1.13) to 1.81 (0.93) when  $N_s$  increases from  $3 \times 10^{19} \text{ cm}^{-3}$  to  $5 \times 10^{19} \text{ cm}^{-3}$ . For the RDD case, this is partially due to the larger number of the doping atom when  $N_s$  is higher, which

reduces the normalized fluctuation of dopants  $N_s$  i.e.,  $\sigma(N)/N = (N_s \times V_{rdd})^{-1/2}$  [21] (where  $V_{rdd}$  is the volume of RDD region), and thus reduce the RDD impact. Additionally, for higher  $N_s$ , the worse SS feature as shown in Fig. 1(c) also contributes to reducing the RDD influence due to the weak dependence of current on the bias and thus the band profile. The latter is also responsible for the reduction of the variation due to WFV under high  $N_s$ . Moreover, the worse SS feature under the higher  $N_s$  also reduces the dependence of  $CV(I_{ds})$  on  $V_{gs}$  since the point SS changes less significantly. It should be noted again that the whole SS characteristic becomes inferior when  $N_s$  is larger as shown in Fig. 1(c), so there exists some trade-off between the switch characteristic and the variability in TFETs when choosing  $N_s$ .

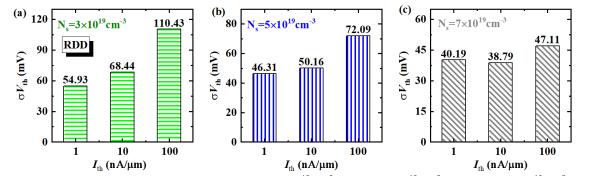

The standard deviation of the threshold voltage  $(V_{th})$  considering RDD and WFV under different threshold current

Fig. 5. Threshold voltage variation considering RDD vs.  $I_{\text{th}}$  under (a)  $N_s = 3 \times 10^{19} \text{cm}^{-3}$ , (b)  $N_s = 5 \times 10^{19} \text{cm}^{-3}$ , and (c)  $N_s = 7 \times 10^{19} \text{cm}^{-3}$  in InAs TFET.

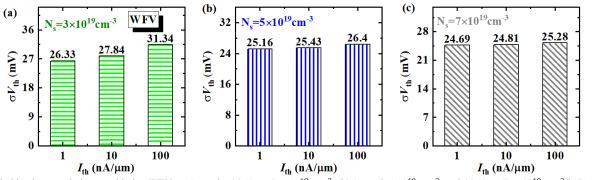

Fig. 6. Threshold voltage variation considering WFV vs.  $I_{\rm th}$  under (a)  $N_s = 3 \times 10^{19} {\rm cm}^{-3}$ , (b)  $N_s = 5 \times 10^{19} {\rm cm}^{-3}$ , and (c)  $N_s = 7 \times 10^{19} {\rm cm}^{-3}$  in InAs TFET.

$(I_{\rm th})$  criteria is shown in Figs. 5 and 6, respectively. For simplicity, the constant current method is used to define  $V_{\rm th}$ , as done in Refs. [8] and [11]. With the increase of  $I_{\rm th}$ ,  $\sigma(V_{\rm th})$ increases under no matter the impact of RDD or WFV. For example,  $\sigma(V_{\rm th})$  induced by RDD is 54.93mV, 68.44mV, and 110.43mV when  $I_{\text{th}}$  is chosen, respectively, at  $\ln A/\mu m$ , 10nA/µm, and 100nA/µm at  $N_{\rm s} = 3 \times 10^{19} {\rm cm}^{-3}$ . The corresponding quantities are reduced to 26.33mV, 27.84mV, and 31.34mV respectively in the WFV case. Because the gate control generally becomes weaker when  $I_{th}$  is higher, it needs more gate voltages to reach the criteria condition when the transfer curve shifts from the nominal one due to the influence of variability. Hence,  $\sigma(V_{\rm th})$  becomes larger with  $I_{\rm th}$ . This suggests that the statistical variation in  $V_{\rm th}$  can be reduced by designing TFET with  $I_{\rm th}$  appearing at the point where gate-control is stronger or point SS is relatively smaller. It can also be found that the dependence of  $\sigma(V_{\text{th}})$  on  $I_{\text{th}}$  also becomes weaker when  $N_s$  varies from  $3 \times 10^{19}$  cm<sup>-3</sup> to  $7 \times 10^{19}$  cm<sup>-3</sup>, as the case in the current variation shown in Figs. 3 and 4, which can also be explained by the previous analyses.

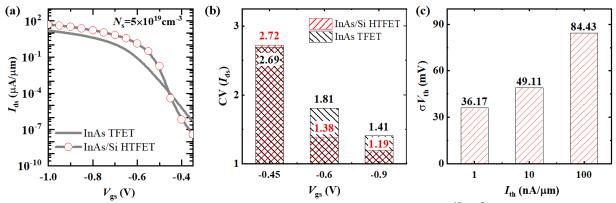

Since the heterostructure can improve the on-state current of TFETs, it is worth investigating the related variabilities in heterojunction TFET (HTFET). Fig. 7(a) shows the nominal  $I_{\rm ds} - V_{\rm gs}$  curve of the InAs/Si HTFET. Figs. 7(b) and 7(c) depict the dependence of variation in  $I_{\rm ds}$  and  $V_{\rm th}$  of HTFET on  $V_{\rm gs}$  and  $I_{\rm th}$  respectively, under the influence of RDD. In the HTFET, the channel and drain materials are Si, and the doping in the drain is  $N_{\rm d} = 2 \times 10^{20} {\rm cm}^{-3}$ . Other device parameters

are the same as those in Fig. 1(a), including the configuration of RDD. As comparison, the corresponding  $I_{ds} - V_{gs}$  curve and current variation of the InAs homojunction TFET from Fig. 1(c) and Fig. 3(b) are also replotted in Fig. 7(a) and (b), respectively. As can be seen from Fig. 7(a), the HTFET not only can deliver high on-current, such as  $I_{\rm ds}$  at  $V_{\rm gs} = -0.9 V$  is  $3.5 \times$  of that in InAs TFET, but also has a steeper switch characteristic [22], [23]. From Figs. 7(b) and 7(c),  $CV(I_{ds})$  also decreases with the decrease of  $V_{gs}$ , and  $\sigma(V_{th})$  increases with the increase  $I_{th}$ . Furthermore, from Fig.7(b), it can be said that the heterostructure is superior to the homostructure in terms of the current variability. The weaker  $I_{ds}$  variability in the HTFET at  $V_{\rm gs}$  of -0.6V and -0.9V can be mainly attributed to its steeper switch characteristic, since then the device is within the weaker gate-control region as shown in Fig. 7(a), and thus the current is less suspectable to the variation in the band profile around tunneling junction. The  $CV(I_{ds})$  at  $V_{gs}$  of -0.45V in the HTFET (2.72) is higher than that in InAs TFET (2.69) but not much although the point SS in the former is much smaller. We believe that it is the band-offset between the source and channel materials that mitigate the severe variation in  $I_{ds}$  at steeper point in HTFET. It should be noted that the offset band is not affected by RDD. Thus, the influence of RDD on the tunneling junction will be partially weakened when the offset-band is within the tunneling window. This means that the band-offset and the consequent stronger gate-control or steeper switch characteristic, lead to opposite effects on the current variability, counteracting each other's influence. As expected, the

Fig. 7. (a) Comparison of the nominal  $I_{ds} - V_{gs}$  curve of InAs/Si HTFET to that of InAs TFET under  $N_s = 5 \times 10^{19} \text{cm}^{-3}$ . (b) Histograms of CV( $I_{ds}$ ) vs.  $V_{gs}$  and (c)  $\sigma(V_{th})$  vs.  $I_{th}$  under the influence of RDD. For simplicity, the CV( $I_{ds}$ ) vs.  $V_{gs}$  data from Fig. 3(b) is also replotted in Fig. 7(b).

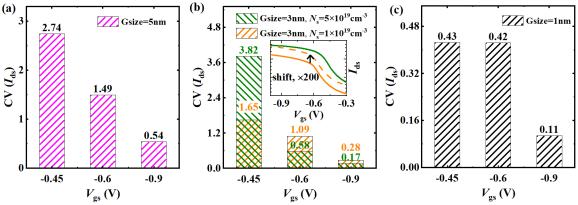

Fig. 8. Dependences of normalized current variation by WFV on gate voltage in InAs/Si HTFET under (a) Gsize = 5nm, (b) Gsize = 3nm, and (c) Gsize = 1 nm.  $N_s$  =  $1 \times 10^{19}$  cm<sup>-3</sup> and  $V_{ds}$  = -1.0V. Fig. 8(b) also shows the case under  $N_s$  =  $5 \times 10^{19}$  cm<sup>-3</sup> to emphasize the influence of band-offset in heterostructure when compared with homostructure. The inset in Fig. 8(b) plots the nominal  $I_{ds} - V_{gs}$  curves of InAs/Si HTFET under  $N_s$  =  $5 \times 10^{19}$  cm<sup>-3</sup> and  $1 \times 10^{19}$  cm<sup>-3</sup>, and the dashed line is just the shifting result for comparison

dependence of  $\sigma(V_{\text{th}})$  on  $I_{\text{th}}$  is also stronger in the HTFET compared with that in the homojunction TFET, by comparing Figs. 5(b) and 7(c).

Considering that the lower grain size can be achieved, such as by incorporation of C or copper into TiN mental to make an amorphous film [5], [24], it is also interesting to study the dependence of FoM on criteria under the influence of WFV with different grain size, especially in the potential HTFET. Fig. 8 shows the histograms of  $CV(I_{ds})$  vs.  $V_{gs}$  under Gsize = 5nm, 3nm, and 1nm in InAs/Si HTFET with  $N_s = 1 \times 10^{19} \text{ cm}^{-3}$ . As previous reported in Refs. [5] and [7], the influence of WFV on  $I_{ds}$  becomes gradually weak as the decrease of grain size due to the lower impact on energy barrier. The experimental result reported in Ref. [25] also confirms that using the amorphous metal gate is effective to suppress the influence of WFV. However, due to the limitation of cost and low deposition rate in atom-layer deposition process, which is suitable for the growth of amorphous metal in nanowire or FinFET structures [26], the conventional physical vapor deposition methods are still used in nanowire [27] despite it having the limitation of conformality and thickness control. This may cause the grown metal materials always composed of several crystal grains with distinct orientations and are not completely amorphous [5], [28], meaning that there are still some influences of WFV even in the "amorphous" case. As can be seen from Fig. 8, the  $CV(I_{ds})$ decreases with  $V_{gs}$  in all cases. Fig. 8(b) also plots the  $CV(I_{ds})$ under  $N_s = 5 \times 10^{19} \text{ cm}^{-3}$  to do indicate the influence of band-offset in heterojunction on the variability. The corresponding nominal  $I_{ds} - V_{gs}$  curves are shown in the inset of Fig. 8(b), and the dashed line shows the result shifting from the data of  $N_s = 1 \times 10^{19} \text{ cm}^{-3}$  just for comparison. It is obvious that the HTFET under  $N_s = 5 \times 10^{19} \text{ cm}^{-3}$  turns on faster than that under  $N_{\rm s} = 1 \times 10^{19} {\rm cm}^{-3}$ . Thus, the much steeper point at  $V_{gs}$  of -0.45V in the former causes the very stronger fluctuation in the current (3.82 vs 1.65 for  $CV(I_{ds})$ ). This is different from the comparison result in Fig. 7(b) with a comparable current variation at  $V_{gs}$  of -0.45V although the SS features are also distinct between the two devices. It should be noted that the two devices in Fig. 8(b) are both heterostructures, meaning that the band-offset is no longer the advantage to the current variability. This demonstrates that the offset-band in the

heterostructure can weaken the variation in the current, especially at the steep point, when compared with homostructure. Different from the case in InAs TFET, the stronger dependence of current variation on gate voltage occurs in the higher  $N_s$  in HTFET from Fig. 8(b), which clarifies that it is the SS characteristic rather than the doping that determine the variability by WFV.

Interface traps are regarded as another important source of variability in TFET. It causes random telegraph noise [29]-[31] and trap-assisted tunneling (TAT) (the scattering influence from trap can be neglected due to TFETs are not sensitive to the mobility fluctuation [32], [33]) [34], [35]. For example, Ref. [36] modeled the influences of interface trap, and found that subthreshold region in transfer characteristics has a severer fluctuation in TFETs due to TAT. The experimental result in Ref. [37] shows that the individual nanowire Tunnel FETs has a significant variability at room temperature due to multiple factors including trap. Although the inclusion of interface trap can improve the reliability of the variability predicted, our purpose is to provide the variation tendency of variability rather than the realistic assessment of variability. Furthermore, the full-quantum simulation with inclusion of interface trap is computationally cumbersome in a large-scale statistical study like this. Thus, the inclusion of interface traps is not considered within our scope and simulation speed limitations. They can be the subject of future work.

#### **IV. CONCLUSION**

The dependences of the variability in p-type nanowire TFETs under the influence of RDD and WFV on the definition of the main FoM have been investigated using quantum transport simulations. The  $I_{ds}$  variation is generally reduced with  $V_{gs}$ , and the  $V_{th}$  variation is increases with  $I_{th}$  due to the gradually deteriorated SS in a TFET. This indicates that the performance variations are directly influenced by the criteria defining the FoM which could be different for different technologies. The dependence of the variability on criteria becomes stronger in the device with better SS characteristic, and the smaller the point SS, the corresponding current variation severer. In order to suppress the performance fluctuation of TFETs, adopting high  $N_s$  and amorphous metal

are effective methods in terms of RDD and WFV source of variability, respectively. Furthermore, it is interesting to find that the performance variation in heterostructure is comparable to that in homostructure although the former has a superior SS characteristic.

### REFERENCES

- A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energy efficient electronic switches," *Nature*, vol. 479, no. 7373, pp. 329–337, Nov. 2011, doi: 10.1038/nature10679.

- [2] S. Yip, L. Shen, and J. C Ho, "Recent advances in III-Sb nanowires: from synthesis to applications," *Nanotechnology*, vol. 30, no. 2, p. 202003, May 2019, doi: 10.1088/1361-6528/aafcce.

- [3] E. Memisevic, J. Svensson, E. Lind, and L.-E. Wernersson, "Impact of source doping on the performance of vertical InAs/InGaAsSb/GaSb nanowire tunneling field-effect transistors," *Nanotechnology*, vol. 29, no. 43, p. 435201, Oct. 2018, doi: 10.1088/1361-6528/aad949.

- [4] G. Espineira, D. Nagy, G. Indalecio, A. J. Garcia-Loureiro, K. Kalna, and N. Seoane, "Impact of gate edge roughness variability on FinFET and gate-all-around nanowire FET," *IEEE Electron Device Lett.*, vol. 40, no. 4, pp. 510–513, Apr. 2019, doi: 10.1109/LED.2019. 2900494.

- [5] N. Thoti, Y. Li, and W. -L. Sung, "Significance of Work Function Fluctuations in SiGe/Si Hetero-Nanosheet Tunnel-FET at Sub-3 nm Nodes," *IEEE Trans. Electron Devices*, vol. 69, no. 1, pp. 434-438, Jan. 2022, doi: 10.1109/TED.2021.3130497.

- [6] J. H. Kim, T. C. Kim, G. Kim, H. W. Kim, and S. Kim, "Methodology to Investigate Impact of Grain Orientation on Threshold Voltage and Current Variability in Tunneling Field-Effect Transistors," *IEEE Journal* of the Electron Devices Society, vol. 8, pp. 1345-1349, 2020, doi: 10.1109/JEDS.2020.3033313.

- [7] Y. Guan, H. Carrillo-Nuñez, V. P Georgiev, A. Asenov, F. Liang, Z. Li, and H. Chen, "Quantum simulation investigation of work-function variation in nanowire tunnel FETs," *Nanotechnology*, vol. 32, no. 15, p. 150001, Apr. 2021, doi: 10.1088/1361-6528/abd125.

- [8] J. Yoon and R. Baek, "Study on Random Dopant Fluctuation in Core-Shell Tunneling Field-Effect Transistors," *IEEE Trans. Electron Devices*, vol. 65, no. 8, pp. 3131-3135, Aug. 2018, doi: 10.1109/TED.2018.2846782.

- [9] Y. Lee, H. Nam, J. Park, and C. Shin, "Study of Work-Function Variation for High-k /Metal-Gate Ge-Source Tunnel Field-Effect Transistors," *IEEE Trans. Electron Devices*, vol. 62, no. 7, pp. 2143-2147, Jul. 2015, doi: 10.1109/TED.2015.2436815.

- [10] Y. Guan, Z. Li, H. Carrillo-Nuñez, V. P. Georgiev, and A. Asenov, "Quantum Mechanical Simulations of the Impact of Surface Roughness on Nanowire TFET performance," International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), 2019, pp. 1-4, doi: 10.1109/SISPAD.2019.8870385.

- [11] H. Carrillo-Nuñez, J. Lee, S. Berrada, C. Medina-Bailón, F. Adamu-Lema, M. Luisier, A. Asenov, and V. P. Georgiev, "Random Dopant-Induced Variability in Si-InAs Nanowire Tunnel FETs: A Quantum Transport Simulation Study," *IEEE Electron Device Lett.*, vol. 39, no. 9, pp. 1473-1476, Sept. 2018, doi: 10.1109/LED.2018.2859586.

- [12] F. Conzatti, M. G. Pala, and D. Esseni, "Surface-Roughness-Induced Variability in Nanowire InAs Tunnel FETs," *IEEE Electron Device Lett.*, vol. 33, no. 6, pp. 806-808, Jun. 2012, doi: 10.1109/LED.2012.2192091.

- [13] C. Hsu, M. Fan, V. P. Hu, and P. Su, "Investigation and Simulation of Work-Function Variation for III–V Broken-Gap Heterojunction Tunnel FET," *IEEE Journal of the Electron Devices Society*, vol. 3, no. 3, pp. 194-199, May 2015, doi: 10.1109/JEDS.2015.2408356.

- [14] K. Nayak, S. Agarwal, M. Bajaj, P. J. Oldiges, K. V. R. M. Murali, and V. R. Rao, "Metal-Gate Granularity-Induced Threshold Voltage Variability and Mismatch in Si Gate-All-Around Nanowire n-MOSFETs," *IEEE Trans. Electron Devices*, vol. 61, no. 11, pp. 3892-3895, Nov. 2014, doi: 10.1109/TED.2014.2351401.

- [15] K. Han, J. Lee, S. Tang, H. Maynard, N. Yoshida, and A. Brand, "FinFET multi-Vt tuning with metal gate work function modulation by plasma doping," International Workshop on Junction Technology (IWJT), 2014, pp. 1-3, doi: 10.1109/IWJT.2014.6842043.

- [16] K. M. Choi, W. -S. Lee, K. -H. Lee, Y. -K. Park, and W. Y. Choi, "Influence of Preferred Gate Metal Grain Orientation on Tunneling FETs," *IEEE Trans. Electron Devices*, vol. 62, no. 4, pp. 1353-1356, April 2015, doi: 10.1109/TED.2015.2399018.

- [17] H. Carrillo-Nuñez, J. Lee, S. Berrada, C. Medina-Bailón, M. Luisier, A. Asenov, and V. P. Georgiev, "Efficient Two-Band based Non-Equilibrium Green's Function Scheme for Modeling Tunneling Nano-Devices," International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), 2018, pp. 141-144, doi: 10.1109/SISPAD.2018.8551629.

- [18] S. Berrada, H. Carrillo-Nunez, J. Lee, C. Medina-Bailon, T. Dutta, O. Badami, F. Adamu-Lema, V. Thirunavukkarasu, V. Georgiev, and A. Aseno, "Nano-electronic Simulation Software (NESS): a flexible nano-device simulation platform," *Journal of Computational Electronics*, vol. 19, pp. 1031-1046, Sept. 2020, doi: 10.1007/s10825-020-01519-0

- [19] S. S. Sylvia, K. M. M. Habib, M. A. Khayer, K. Alam, M. Neupane, and R. K. Lake, "Effect of Random, Discrete Source Dopant Distributions on Nanowire Tunnel FETs," *IEEE Trans. Electron Devices*, vol. 61, no. 6, pp. 2208-2214, June 2014, doi: 10.1109/TED.2014.2318521.

- [20] A.Pan and C. On Chui, "Modeling direct interband tunneling. II. Lower-dimensional structures," J. App. Phys., vol. 116, p. 054509, Aug. 2014, doi:10.1063/1.4891528

- [21] G. Leung and C. O. Chui, "Stochastic Variability in Silicon Double-Gate Lateral Tunnel Field-Effect Transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 1, pp. 84-91, Jan. 2013, doi: 10.1109/TED.2012.2226725.

- [22] W. Li and J. C. S. Woo, "Vertical P-TFET With a P-Type SiGe Pocket," *IEEE Trans. Electron Devices*, vol. 67, no. 4, pp. 1480-1484, April 2020, doi: 10.1109/TED.2020.2971475.

- [23] G. Dewey, B. Chu-Kung, J. Boardman, J. M. Fastenau, J. Kavalieros, R. Kotlyar, W. K. Liu, D. Lubyshev, M. Metz, N. Mukherjee, P.Oakey, R. Pillarisetty, M. Radosavljevic, H. W. Then, and R. Chau, "Fabrication, characterization, and physics of III–V heterojunction tunneling Field Effect Transistors (H-TFET) for steep sub-threshold swing," International Electron Devices Meeting (IEDM), 2011, pp. 33.6.1-33.6.4, doi: 10.1109/IEDM.2011.6131666.

- [24] J. L. He, Y. Setsuhara, I. Shimizu, and S. Miyake, "Structure refinement and hardness enhancement of titanium nitride films by addition of copper," *Surf. Coat. Technol.*, vol. 137, no. 1, pp. 38-42, Mar. 2001, doi: 10.1016/S0257-8972(00)01089-6.

- [25] T. Matsukawa, Y. X. Liu, W. Mizubayashi, J. Tsukada, H. Yamauchi, K. Endo, Y. Ishikawa, S. O'uchi, H. Ota, S. Migita, Y. Morita, and M. Masahara, "Suppression of threshold voltage variability of double-gate fin field-effect transistors using amorphous metal gate with uniform work function," *Appl. Phys. Lett.* vol. 102, p. 162104, Apr. 2013, doi: 10.1063/1.4803040.

- [26] T. Nam, C. Lee, T. Cheon, W. Lee, S.-H. Kim, S-H. Kwon, H.-B.-R. Lee, and H. Kim, "Cobalt titanium nitride amorphous metal alloys by atomic layer deposition," *Journal of Alloys and Compounds*, vol. 737, pp. 684-692, Dec. 2018, doi: 10.1016/j.jallcom.2017.12.023.

- [27] R. Lee, J. Lee, K. Lee, S. Kim, H. Ahn, S. Kim, H.-M. Kim, C. Kim, J.-H. Lee, S. Kim, and B.-G. Park, "Vertically-Stacked Si0.2Ge0.8 Nanosheet Tunnel FET With 70 mV/Dec Average Subthreshold Swing," *IEEE Electron Device Lett.*, vol. 42, no. 7, pp. 962-965, Jul. 2021, doi: 10.1109/LED.2021.3079246.

- [28] R. Wongpiya, J. Ouyang, C.-J. Chung, D. T. Duong, M. Deal, Y. Nishi, and B. Clemens, "Structural and electrical characterization of CoTiN metal gates," *J. Appl. Phys.*, vol. 117, p. 075304, Feb. 2015, doi: 10.1063/1.4908547.

- [29] M.-L. Fan, V. P.-H. Hu, Y.-N. Chen, P. Su and C.-T. Chuang, "Analysis of Single-Trap-Induced Random Telegraph Noise and its Interaction With Work Function Variation for Tunnel FET," *IEEE Trans. Electron Devices*, vol. 60, no. 6, pp. 2038-2044, June 2013, doi: 10.1109/TED.2013.2258157.

- [30] C. Chen, Q. Huang, J. Zhu, Y. Zhao, L. Guo and R. Huang, "New Understanding of Random Telegraph Noise Amplitude in Tunnel FETs," *IEEE Trans. Electron Devices*, vol. 64, no. 8, pp. 3324-3330, Aug. 2017, doi: 10.1109/TED.2017.2712714.

- [31] S. Chander, S. K. Sinha, and R. Chaudhary, "Comprehensive review on electrical noise analysis of TFET structures," *Superlattice. Microst.*, vol. 161, p. 107101, Dec. 2021, doi: 10.1016/j.spmi.2021.107101.

- [32] Y. Qiu, R. Wang, Q. Huang and R. Huang, "A Comparative Study on the Impacts of Interface Traps on Tunneling FET and MOSFET," *IEEE Trans. Electron Devices*, vol. 61, no. 5, pp. 1284-1291, May 2014, doi: 10.1109/TED.2014.2312330.

- [33] J. Knoch and J. Appenzeller, "Tunneling phenomena in carbon nanotube field-effect transistors," Physica Status Solidi (a), vol. 205, no. 4, pp. 679–694, Jan. 2008, doi: 10.1002/pssa.200723528.

- [34] R. Pandey, S. Mookerjea and S. Datta, "Opportunities and Challenges of Tunnel FETs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 63, no. 12, pp. 2128-2138, Dec. 2016, doi: 10.1109/TCSI.2016.2614698.

- [35] S. Sant and A. Schenk, "Trap-Tolerant Device Geometry for InAs/Si pTFETs," *IEEE Electron Device Lett.*, vol. 38, no. 10, pp. 1363-1366, Oct. 2017, doi: 10.1109/LED.2017.2740262.

- [36] D. Esseni and M. G. Pala, "Interface Traps in InAs Nanowire Tunnel FETs and MOSFETs—Part II: Comparative Analysis and Trap-Induced Variability," *IEEE Trans. Electron Devices*, vol. 60, no. 9, pp. 2802-2807, Sept. 2013, doi: 10.1109/TED.2013.2274197.

- [37] T. Rosca, A. Saeidi, E. Memisevic, L. Wernersson and A. M. Ionescu, "An Experimental Study of Heterostructure Tunnel FET Nanowire Arrays: Digital and Analog Figures of Merit from 300K to 10K," International Electron Devices Meeting (IEDM), 2018, pp. 13.5.1-13.5.4, doi: 10.1109/IEDM.2018.8614665.