Mohamed, A., Wagner, M., Heidari, H. and Anders, J. (2022) A frontend for magnetoresistive sensors with a  $2.2 \text{ pA}/\sqrt{\text{Hz}}$  low-noise current source. IEEE Solid-State Circuits Letters, (doi: 10.1109/LSSC.2022.3148362).

There may be differences between this version and the published version. You are advised to consult the publisher's version if you wish to cite from it.

https://eprints.gla.ac.uk/264486/

Deposited on: 31 January 2022

Enlighten – Research publications by members of the University of Glasgow <a href="https://eprints.gla.ac.uk">https://eprints.gla.ac.uk</a>

# A frontend for magnetoresistive sensors with a 2.2 pA/ $\sqrt{\text{Hz}}$ low-noise current source

Ayman Mohamed, Student, IEEE, Marco Wagner, Hadi Heidari, Senior, IEEE and Jens Anders Senior, IEEE.

Abstract—In this letter, we present an integrated readout chip for magnetoresistive (MR) sensors consisting of a readout chain that comprises a DC-coupled fully differential difference amplifier (FDDA) followed by a programmable gain amplifier (PGA), as well as a low-noise current biasing scheme for the MR sensor. The current bias scheme features a 10-bit digital-to-analog converter (DAC) to compensate for process variations of the MR sensing element as well as to calibrate for variations in the DC bias field of the sensor. The bias current source achieves a very low current noise floor of  $2.2\,\mathrm{pA}/\sqrt{\mathrm{Hz}}$  for bias currents up to 1 mA showing a 5x improvement compared to prior arts. The readout chip is manufactured in 180 nm SOI CMOS and consumes a total power of 38 mW. The paper is an extended version of [8], incorporating additional modeling details and measurement results.

### I. INTRODUCTION

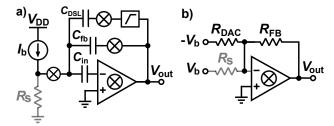

Many emerging biosensing applications [1], [2] as well as human machine interfaces for augmented reality applications [3] rely on giant magnetoresistive (GMR) sensors due to their good sensitivity and low 1/f noise. As an alternative, tunnel magnetoresistive (TMR) sensors can provide superior sensitivity compared to GMR sensors due to their higher magnetoresistive (MR) ratios. However, such high MR ratios impose strict requirements on the interface electronics due to the large variations in their base resistance. Such variations lead to large voltage offsets at the amplifier input, reducing the dynamic range of the amplifier, and, in the worst case, saturating the frontend if uncompensated. A possible solution to eliminate the input DC offset of the amplifier is to use a chopped capacitively-coupled instrumentation amplifier (CCIA) in combination with a DC servo loop (DSL) [4], cf. Fig. 1a. However, this approach presents a tradeoff between the input-referred voltage noise of the amplifier and the maximum offset that the DSL can compensate. More specifically, a higher input offset can be compensated by increasing  $C_{\rm DSL}$ , which, in turn, increases the input-referred voltage noise of the CCIA [5]. As an alternative, Fig. 1b shows the possibility of using a voltage bias across the MR element in combination with a transimpedance amplifier (TIA) to process the resulting current [2]. In this scheme, frequently, an auxiliary resistive

Manuscript received Dec. 2, 2021. This work is supported by the Carl Zeiss Foundation and the German Research Foundation (DFG) under contract no. AN 984/12-1.

Ayman Mohamed, Marco Wagner and Jens Anders are with the Institute of Smart Sensors, University of Stuttgart, D-70569 Stuttgart, Germany (e-mail: ayman.mohamed@iis.uni-stuttgart.de).

Ayman Mohamed and Jens Anders are with the Center for Integrated Quantum Science and Technology ( ${\rm IQ^{ST}}$ ), Stuttgart and Ulm, Germany

Hadi Heidari is with the Microelectronics Lab (meLAB), School of Engineering, University of Glasgow, Glasgow, UK

Fig. 1: Block diagram of a) a CCIA frontend with embedded DSL and b) a TIA readout with a resistive DAC.

DAC is added at the virtual ground node to source or sink the DC current generated by the base resistance and offsets. While this scheme is simple, it displays inferior linearity compared to a current bias with voltage readout since the change in resistance occurs in the denominator of the TIA output voltage [2]. Consequently, the linearity can be improved using a current bias followed by a voltage amplifier [1], [6]-[8]. In order to avoid the tradeoff between offset and noise as it occurs in the case of DSLs embedded inside CCIAs as well as the non-linearity problem associated with a voltage bias and TIA readout, in this paper, we implement the offset compensation prior to the amplification stage with an adjustable current biasing using a 10-bit binary-weighted current digital-to-analog converter (DAC) with a large dynamic range. A voltage-mode readout using a fully differential-difference amplifier (FDDA) followed by a programmable gain amplifier (PGA) amplifies the voltage signal at the sensor output, providing a spectrally purer readout compared to a current readout implementation. The presented design is optimized for TMR sensors but can also be used for different MR sensors. This letter, which is an extended version of [8], providing more modeling details and additional measurement results, is organized as follows: In section II, the architecture of the proposed chip is introduced. Section III presents the measurement results of the readout chip. The paper concludes with a summary in section IV.

## II. CHIP DESCRIPTION

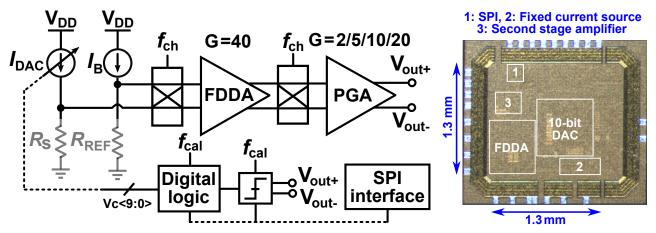

Fig. 2 shows the block diagram of the presented readout ASIC, consisting of the current bias of the sensor and the subsequent voltage amplifiers, together with the chip micrograph [8]. An on-chip fixed current source and an adjustable current DAC bias the MR sensor and a reference resistor, respectively. This differential readout scheme improves the baseline-to-signal-ratio [7]. The compensation of the offset between the sensor and the reference resistor is achieved by continuously monitoring the difference between the MR and the reference resistor output voltages using a DC-coupled

Fig. 2: a) System level block diagram of the readout chip. b) Chip micrograph.

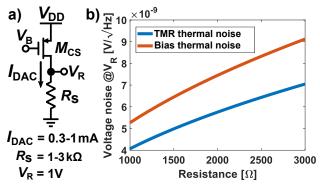

Fig. 3: a) A simple implementation of a PMOS current source biasing an MR sensor. b) Voltage noise at  $V_{\rm R}$  due to the thermal noise of the TMR sensor and the current bias.

readout circuit formed by an FDDA and a PGA, which feeds a dynamic comparator followed by a digital logic that finds the DAC digital codeword necessary to compensate the offset. The automatic compensation routine is triggered via an on-chip SPI interface.

### A. Sensor biasing

A simple implementation of a current bias of a resistor is shown in Fig 3a, where a PMOS transistor in saturation region is used to bias the MR sensor. To account for the large manufacturing tolerances of TMR resistors  $(1 \,\mathrm{k}\Omega$  up to  $3 \,\mathrm{k}\Omega$  for the TMR used in [8]),  $I_{\mathrm{DAC}}$  has to be adjustable. The voltage across the sensor  $V_{\mathrm{R}}$  should be maximized for a given supply voltage, breakdown voltage of the utilized sensor and its passivation layer to optimize the SNR of the sensor [1]. Here, we target  $V_{\mathrm{R}}=1\,\mathrm{V}$  by making  $I_{\mathrm{DAC}}$  adjustable between 0.3 mA and 1 mA. The voltage noise power spectral density (PSD) at  $V_{\mathrm{R}}$ , ignoring flicker noise of the MR sensor, is given by:

$$\begin{split} S_{\Delta V_{\rm R,OL}}^2 &= 4kTR_{\rm s} + S_{\Delta I_{\rm nD,OL}^2} \cdot R_{\rm s}^2, \\ S_{\Delta I_{\rm nD,OL}^2} &= 4kT\gamma g_{\rm m} + \frac{{\rm KF} \cdot g_{\rm m}^2}{C_{\rm ox} \cdot W \cdot L \cdot f}, \end{split} \tag{1}$$

where  $S_{\Delta I_{\rm nD,OL}^2}$  is the current noise PSD of  $M_{\rm CS}$ , k is the Boltzmann constant, T is absolute temperature,  $\gamma$  is the excess noise factor,  $g_{\rm m}$  is the transconductance of transistor  $M_{\rm CS}$ ,

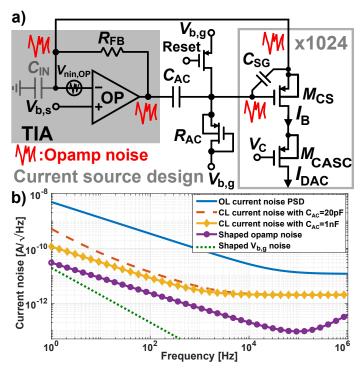

KF is the flicker noise factor,  $C_{ox}$  is the oxide capacitance per unit area and W and L are the transistor width and length, respectively. The first summand of eq. (1) models the thermal noise of the MR sensor while the second and third summand model the thermal and flicker noise of the transistor  $M_{\rm CS}$ . The voltage noise PSD can be lowered by biasing the transistor  $M_{\rm CS}$  deeply in strong inversion, where  $g_{\rm m} = 2 \cdot I_{\rm DAC}/V_{\rm ds,sat}$ and  $V_{\rm ds,sat}$  is limited by the available voltage overhead of  $V_{\rm DD}-V_{\rm R}$  and/or the onset of velocity saturation effects. For a supply voltage of 1.8 V and a voltage drop across the resistor of  $V_{\rm R} = 1 \, \rm V$ , the maximum voltage headroom for the transistor is given by 0.8 V. Fig. 3b shows the thermal noise floor of both the MR sensor and the current source according to eq. (1) for  $V_{\rm DD} = 1.8 \, {\rm V}, \ V_{\rm R} = 1 \, {\rm V}$  and the process parameters of the 180 nm CMOS process used for the chip implementation described in section III, as a function of the sensor resistance  $R_{\rm s}$ . Clearly, the thermal noise floor of the current bias dominates the MR noise, and hence degrades the intrinsic SNR of the MR sensor. As a possible route to lowering the noise of the current source transistor  $M_{\rm CS}$ , in this paper, we follow the idea of [1] and [6] of embedding the transistor  $M_{\rm CS}$  into a feedback loop. However, in contrast to [1], [6], the feedback loop used in this work, cf. Fig. 4a, utilizes a TIA to reduce noise-induced fluctuations in the output current [8]. Importantly, the TIA architecture greatly reduces the influence of the opamp noise on the overall current noise compared to previously presented noise reduction loops [1], [6]. The TIA-based feedback loop works as follows. Overall, the feedback loop regulates the source-gate voltage  $v_{\rm sg}$  of transistor  $M_{\rm CS}$  with a high loop gain to reduce noiseinduced fluctuations in the output current. The virtual short at the opamp input causes the source of transistor  $M_{\rm CS}$  to be biased at  $V_{\rm DD}$ . The bias current flows through the TIA feedback resistor  $R_{\rm FB}$ , producing a proportional voltage at the TIA output, which counteracts fluctuations in the output current. To allow for adjusting the DC bias current using the on-chip generated bias voltage  $V_{\rm B}$ , the TIA output is AC coupled to the gate of  $M_{CS}$ , cf. Fig. 4a, effectively high pass filtering the TIA output with a very low cut-off frequency formed by capacitor  $C_{\rm AC}=20\,{\rm pF}$  and pseudoresistor  $R_{\rm AC} = 10 \, {\rm G}\Omega$ . Additionally, a reset switch is added to the gate of the transistor M<sub>CS</sub> to reset this high impedance node

Fig. 4: a) Block diagram of the proposed current bias. b) Simulated current noise PSD of the current bias with and without the feedback loop.

if necessary. In [8], we provided a simplified noise analysis of the circuit of Fig. 4a that neglected second-order effects such as the voltage divider between  $C_{\rm AC}$  and  $C_{\rm SG}$  as well as the effect of the finite channel conductance  $g_{\rm ds}$ , of transistor  $M_{\rm CS}$ , on the overall noise performance. Here, we specifically account for these two effects, and the resulting output current noise PSD of the proposed current source is given by:

$$S_{\Delta I_{\rm nD,CL}^{2}} \approx \frac{S_{\Delta I_{\rm nD,OL}^{2}}}{(1 + g_{\rm m}R_{\rm FB}x_{\rm div})^{2}} + \frac{4kT}{R_{\rm FB}}$$

$$+ \left[ S_{\Delta V_{\rm nin,OP}^{2}} + S_{\Delta V_{\rm b,s}^{2}} \right] \left[ \frac{g_{\rm ds} - j\omega g_{\rm m}R_{\rm FB}C_{\rm in}x_{\rm div}}{1 + g_{\rm m}R_{\rm FB}x_{\rm div}} \right]^{2}$$

$$+ S_{\Delta V_{\rm b,s}^{2}} \left[ \frac{g_{\rm m}}{1 + j\omega R_{\rm AC}C_{\rm AC}(1 + g_{\rm m}R_{\rm FB})} \right]^{2},$$

(2)

where  $x_{\rm div} = C_{\rm AC}/\left(C_{\rm AC} + C_{\rm SG}\right)$  and  $C_{\rm IN}$  is the opamp input capacitance. Here, it is important to point out that, in contrast to the open-loop case, increasing  $g_{\rm m}$  improves the overall noise performance by increasing the loop gain, cf. eq. (1). Hence, the scheme of Fig. 4a favors an operation of transistor  $M_{\rm CS}$  in weak inversion, drastically reducing the headroom requirements for the current source. Moreover, any noise originating in the opamp of the TIA is greatly suppressed by the feedback loop of Fig. 4a, cf. eq. (2). Intuitively, at low frequencies, the TIA provides a voltage gain of unity from its input-referred voltage noise to the TIA output voltage, i.e. the gate voltage of transistor  $M_{\rm CS}$ . Moreover, the virtual short at the TIA input causes the source voltage of  $M_{\rm CS}$  to also equal the TIA's input-referred voltage noise as depicted by the noise signals in Fig. 4a. Therefore, any noise originating in the TIA opamp does not change the source-gate voltage

$v_{\rm sg}$  of transistor  $M_{\rm CS}$  and, therefore, does not increase the output current noise. However, the finite output conductance,  $g_{\rm ds}$ , of  $M_{\rm CS}$  prevents a complete cancelation of the internal opamp and opamp bias voltage noise  $V_{\rm b,s}$ , even at DC. At higher frequencies, the voltage divider between  $R_{\rm FB}$  and  $C_{\rm in}$ further deteriorates the cancelation of the opamp internal and bias noise, producing a noise contribution that increases with 20 dB/dec. It is worth mentioning that the overall noise of the opamp is typically still negligible compared to the noise of  $M_{\rm CS}$ , cf. Fig 4b. Importantly, according to eq. (2), for a proper noise reduction, the value of the AC coupling capacitor  $C_{\rm AC}$  has to be chosen sufficiently larger than the gate source capacitance of  $M_{\rm CS}$ ,  $C_{\rm sg}$ . The gate bias voltage,  $V_{\rm b,g}$ , is low-pass filtered with a very low corner frequency, rendering its noise contribution negligible. Fig. 4b shows the simulated current noise PSD for an output current of 1 mA and a TIA feedback resistor of  $R_{\rm FB}=4\,{\rm k}\Omega.$  According to eq. (2), the open-loop current noise PSD of transistor  $M_{\rm CS}$ ,  $S_{\Delta I_{\rm nD,OL}^2}$ , is reduced by the loop gain  $g_{\rm m}R_{\rm FB}x_{\rm div}$ . The closed-loop noise floor is established by the current noise of the feedback resistor  $R_{\rm FB}$ , cf. eq. (2), and given by  $2 \, {\rm pA/\sqrt{Hz}}$  for the  $4 \, {\rm k}\Omega$  resistor used in the presented design. According to Fig. 4b, assuming a fairly large bias voltage noise of  $S_{\Delta V_{\rm b,g}} = 100\,\mathrm{nV}/\mathrm{VHz}$ , for frequencies above 1 Hz, the resulting current noise is still negligible. Moreover, the shaped opamp, assuming an input-referred opamp noise of  $80 \,\mathrm{nV/VHz}$ , is also negligible compared to the closed-loop noise of  $M_{\rm CS}$  up to frequencies beyond 1 MHz.

# B. Amplifier implementation

According to Fig. 2a, the low-noise bias current  $I_{\rm DAC}$  flows through the TMR sensor and produces a voltage signal which is subsequently amplified by a fully differential-difference amplifier (FDDA) followed by a programmable gain amplifier (PGA). In the presented design, the FDDA has a fixed gain of 40 and the PGA features four different gain settings to accommodate different dynamic range requirements. In order to lower the power consumption of the FDDA while maintaining a good noise performance, the input differential pair is implemented using stacked PMOS and NMOS pairs [9]. Moreover, chopping switches are incorporated into the FDDA to suppress its flicker noise and offset.

# III. MEASUREMENT RESULTS

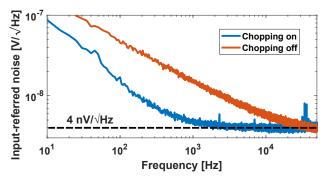

The chip is manufactured in  $180\,\mathrm{nm}$  SOI CMOS and occupies an active area of  $1.7\,\mathrm{mm^2}$ . The presented readout chain consumes  $10.4\,\mathrm{mW}$  from a  $1.8\,\mathrm{V}$  supply while the entire chip, including the MR and reference resistor bias, consumes  $38\,\mathrm{mW}$  from  $3.6\,\mathrm{V}$  and  $6.8\,\mathrm{V}$  supplies [8]. The measured input-referred noise of the readout electronics with and without chopping ( $f_{\rm ch}=60\,\mathrm{kHz}$ ) and with nominally identical ohmic resistors connected to the input is shown in Fig. 5. In both cases, the measured noise floor is  $4\,\mathrm{nV}/\sqrt{\mathrm{Hz}}$ . With enabled chopping, the 1/f-noise corner frequency improves from  $10\,\mathrm{kHz}$  to  $400\,\mathrm{Hz}$ . The residual flicker noise after chopping originates from the unchopped PGA, cf. Fig. 2a. To demonstrate the effectiveness of the presented biasing

Fig. 5: Measured input-referred voltage noise PSD of the amplifier chain without and with chopping at 60 kHz.

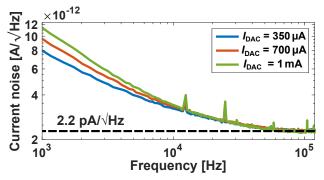

Fig. 6: Measured current noise PSD of  $I_{\rm DAC}$  for different current settings.

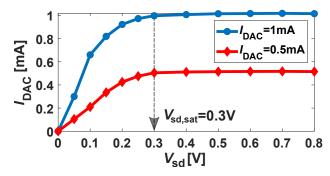

scheme, Fig. 6 shows the measured closed-loop output noise of transistor  $M_{\rm CS}$  for bias currents of  $350\,\mu{\rm A},700\,\mu{\rm A}$  and 1 mA. The measured noise floor is  $2.2 \,\mathrm{pA/\sqrt{Hz}}$  with activated control loop and is defined by the feedback resistor  $R_{\rm FB}$  for all current settings. A slight increase in the flicker noise is observed for higher currents due to the larger  $C_{SG}$  associated with a larger effective device area used for larger currents. Hence, the factor  $x_{\text{div}}$  is reduced for higher currents, and, as a result, the low-frequency noise is slightly increased, cf. eq. (2) and Fig. 4b. The measured current noise floor presents a 5x improvement compared to previous designs [1], [6]. The output characteristics of the current source for  $I_{DAC} = 500 \,\mu\text{A}$ and  $I_{\rm DAC} = 1 \, \rm mA$  is measured in Fig. 7. Despite the verylow noise operation of the designed current source, it can operate with a  $V_{\rm SD}$  as low as  $0.3\,\mathrm{V}$  for different  $I_{\rm DAC}$ . Table I compares this work to the state-of-the-art in MR frontends with current biasing as well as a commercial adjustable very low-noise current source [10].

# IV. CONCLUSION

In this letter, we have presented a combined bias and readout chip for MR sensors. The current bias achieves a state-of-theart noise floor of  $2.2\,\mathrm{pA/\sqrt{Hz}}$  for currents up to  $1\,\mathrm{mA}$ . Its large bias range accommodates the high process variations of TMR sensors. Moreover, the proposed current bias can provide a very low noise floor while operating at a large  $g_\mathrm{m}/I_\mathrm{D}$ , i.e. low  $V_\mathrm{ds,sat}$ . The included programmable readout chain including chopping displays a low noise floor of  $4\,\mathrm{nV/\sqrt{Hz}}$  together with a low 1/f-noise corner of 400 Hz, rendering the overall MR frontend a very versatile and high-performance platform for next-generation MR sensing systems.

Fig. 7: Measured output characteristics of  $I_{\rm DAC}$  for different current settings.

TABLE I: Comparison against the state-of-the-art.

|                         | LM134           | Costa    | Zhou                  | This work  |

|-------------------------|-----------------|----------|-----------------------|------------|

|                         | TI [10]         | TBCAS'17 | JSSC'21               |            |

| Current bias            | up to 10 mA     | 0.5 mA   | _                     | up to 1 mA |

| Bias noise floor        |                 |          |                       |            |

| $[pA/\sqrt{Hz}]$        | $100^{\alpha}$  | 10       | $\approx 10^{\gamma}$ | 2.2        |

| Power [mW]              | _               | 4.9*     | 2.5*                  | 10.4*§/38  |

| Area [mm <sup>2</sup> ] | _               | 3.17     | 1.92                  | 1.7        |

| Min. $V_{\rm ds}$ [V]   | $0.85^{\alpha}$ | _        | -                     | 0.3        |

| Process [µm]            | _               | 0.35     | 0.18                  | 0.18       |

\*Power excludes the current bias. \(^{\gamma}\) Calculated from figures and text.

### REFERENCES

- [1] X. Zhou, E. Mai, M. Sveiven, C. Pochet, H. Jiang, C. C. Huang, and D. A. Hall, "A 9.7-nTrms, 704-ms Magnetic Biosensor Front-End for Detecting Magneto-Relaxation," *IEEE Journal of Solid-State Circuits*, pp. 1–1, 2021.

- [2] D. A. Hall, R. S. Gaster, K. A. A. Makinwa, S. X. Wang, and B. Murmann, "A 256 Pixel Magnetoresistive Biosensor Microarray in 0.18 μm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 48, no. 5, pp. 1290–1301, 2013.

- [3] J. Ge, X. Wang, M. Drack, O. Volkov, M. Liang, G. S. Cañón Bermúdez, R. Illing, C. Wang, S. Zhou, J. Fassbender, M. Kaltenbrunner, and D. Makarov, "A bimodal soft electronic skin for tactile and touchless interaction in real time," *Nature Communications*, vol. 10, no. 1, pp. 1–10, 2019.

- [4] H. Jiang, S. Nihtianov, and K. A. A. Makinwa, "An Energy-Efficient 3.7-nV/√Hz Bridge Readout IC With a Stable Bridge Offset Compensation Scheme," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 3, pp. 856–864, 2019.

- [5] T. Denison, K. Consoer, W. Santa, A.-T. Avestruz, J. Cooley, and A. Kelly, "A 2 μW 100 nV/rtHz Chopper-Stabilized Instrumentation Amplifier for Chronic Measurement of Neural Field Potentials," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 12, pp. 2934–2945, 2007.

- [6] T. Costa, F. A. Cardoso, J. Germano, P. P. Freitas, and M. S. Piedade, "A Cmos Front-End With Integrated Magnetoresistive Sensors for Biomolecular Recognition Detection Applications," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 11, no. 5, pp. 988–1000, 2017.

- [7] X. Zhou, M. Sveiven, and D. A. Hall, "A CMOS Magnetoresistive Sensor Front-End With Mismatch-Tolerance and Sub-ppm Sensitivity for Magnetic Immunoassays," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 13, no. 6, pp. 1254–1263, 2019.

- [8] A. Mohamed, H. Heidari, and J. Anders, "A readout circuit for tunnel magnetoresistive sensors employing an ultra-low-noise current source," in ESSCIRC 2021 - IEEE 47th European Solid State Circuits Conference (ESSCIRC), 2021, pp. 331–334.

- [9] M. Bazes, "Two novel fully complementary self-biased CMOS differential amplifiers," *IEEE Journal of Solid-State Circuits*, vol. 26, no. 2, pp. 165–168, 1991.

- [10] LM134/LM234/LM334 3-Terminal Adjustable Current Sources, Texas Instruments, 5 2013.

<sup>§</sup>Power measured while switching off the sensor bias. For 1 mA current.