Dutta, T., Georgiev, V. and Asenov, A. (2020) Vmin Prediction for Negative Capacitance MOSFET based SRAM. In: 2020 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), 01-30 Sep 2020, ISBN 9781728187655.

There may be differences between this version and the published version. You are advised to consult the publisher's version if you wish to cite from it.

http://eprints.gla.ac.uk/236451/

Deposited on: 15 March 2021

# $V_{\min}$ Prediction for Negative Capacitance MOSFET based SRAM

Tapas Dutta

Device Modeling Group

University of Glasgow

Glasgow, G128LT, UK

tapas.dutta@glasgow.ac.uk

Vihar Georgiev

Device Modeling Group

University of Glasgow

Glasgow, G128LT, UK

vihar.georgiev@glasgow.ac.uk

Asen Asenov

Device Modeling Group

University of Glasgow

Glasgow, G128LT, UK

asen.asenov@glasgow.ac.uk

Abstract—In this work we show that SRAM cells designed using negative capacitance (NC) based MOSFETs (NCFETs) can offer improved  $V_{\min}$  (minimum supply voltage needed for reliable operation) compared to conventional MOSFET based SRAM. Increased noise margins and reduced variability in NCFETs lead to this lowering of  $V_{\min}$ . For this work we use a modified version of the standard BSIM4 compact model for bulk MOSFETs by coupling it with the Landau-Khalatnikov model of ferroelectrics in a self-consistent manner, while the statistical variability information of the reference device is extracted from 3D statistical TCAD simulations.

Keywords—Negative Capacitance, MOSFET, SRAM, n-curve,  $V_{\min}$ , variability

### I. INTRODUCTION

Different approaches have been in vogue for countering the slow scaling of SRAMs in the sub-100 nm regime. SRAM designs based on new transistor architectures have been researched extensively during the last decade with a number of optimizations proposed taking a device-circuit codesign approach [1], [2]. In the mean time, in recent years negative capacitance effect of ferroelectrics has been utilized to enhance the performance of CMOS devices, enabling more aggressive supply voltage  $(V_{\rm DD})$  scaling due to the possibility of achieving sub-60mV subthreshold swings [3]–[5].

Accordingly, various modeling approaches and the impact of improved transistor characteristics on circuits have been reported [6]. In particular, performance of 7nm node NC-FinFET based SRAM was reported in [7]. Further, NC transistors have been shown to offer variability suppression [8]–[10] which is expected to improve the minimum supply voltage for SRAM operation. In this work we examine the SRAM stability through circuit simulations using a compact model of NCFETs.

# II. METHODOLGY AND MODELING APPROACH

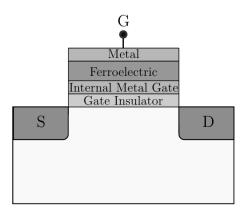

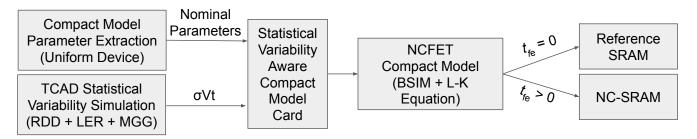

Fig. 1 shows the cross-sectional schematic of the NCFET. The ferroelectric layer is deposited between the internal gate of the baseline MOSFET and an external metal gate. Table I lists some of the structural details of the device. Fig. 2 describes the overall methodology of this work. We start with the extraction of the compact model from the TCAD simulation of the variability-free device. We then perform 3D statistical TCAD simulations of the reference MOSFET

Fig. 1. Cross-sectional schematic of the NCFET. The bulk MOSFET is "well" designed with a gate length of 25nm.

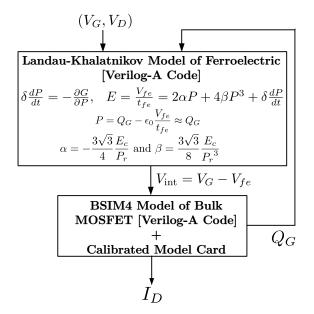

using GARAND [11] considering the three major sources of statistical variability: RDD (random discrete dopants), LER (line edge roughness), and MGG (metal gate granularity). The key parameters used in the statistical simulation are included in Table I. From the statistical ensemble, we obtain the variability in the threshold voltage,  $\sigma Vt$ , which together with the nominal model parameters leads to variability aware compact model card. Next, these parameters are fed to the NCFET model. The compact modeling approach using a self-consistent coupling of the BSIM4 model [12] with the ferroelectric model [13] has been illustrated in Fig. 3. A ferroelectric thickness  $(t_{fe})$  of zero corresponds to the reference bulk MOSFET.

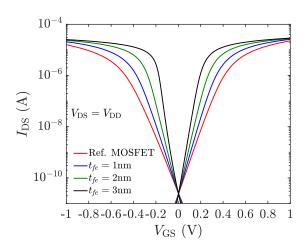

### A. Nominal Device Characteristics

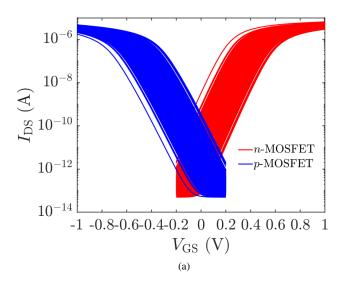

Fig. 4 shows the transfer characteristics of the reference MOSFET and NCFETs (with different  $t_{fe}$ ). The NCFET devices show superior characteristics with steeper subthreshold swing and higher drive current compared to the reference MOSFET for the same OFF-state leakage. Note that for the ferroelectric parameters and the thickness of the ferroelectric layer used in this work, the nominal devices are hysteresis-free.

### B. Variability Suppression

The improved electrostatics in NCFETs leads to a suppression of statistical variability. This has been shown using TCAD simulations as well as compact modeling approaches. In this work, for simplicity we have focused on the variation

Fig. 2. Flow of the overall methodology used in this work. A ferroelectric thickness,  $t_{fe}$  of zero corresponds to the reference bulk MOSFET.

TABLE I. DEVICE DETAILS

| Parameter                   | Value                              |

|-----------------------------|------------------------------------|

| (a) Reference MOSFET        |                                    |

| $L_{ m gate}$               | 25 nm                              |

| $W_{ m gate}$               | 25 nm                              |

| EOT                         | 1 nm                               |

| $N_A$                       | $5 \times 10^{17} \text{ cm}^{-3}$ |

| $N_{S/D}$                   | $1 \times 10^{20} \text{ cm}^{-3}$ |

| (b) Ferroelectric Layer     |                                    |

| $t_{fe}$                    | 1-3 nm                             |

| $P_r$                       | $5 \ \mu\text{C/cm}^2 \ [14]$      |

| $E_c$                       | 1 MV/cm [14].                      |

| (c) Statistical Variability |                                    |

| LER correlation length      | 25 nm                              |

| LER RMS amplitude           | 0.66                               |

| MGG                         | TiN gate (Two W.F. distributions   |

|                             | with 40% and 60% probability)      |

Fig. 3. Compact Modeling Approach. P= polarization, G= total free energy, E= electric field,  $V_{fe}=$  voltage drop across the ferroelectric,  $t_{fe}=$  ferroelectric thickness,  $\delta=$  ferroelectric damping factor,  $Q_G=$  gate charge,  $\alpha$  and  $\beta$ : Landau parameters,  $E_c=$  coercive field,  $P_r=$  remnant polarization.

Fig. 4.  $I_{\rm DS}-V_{\rm GS}$  characteristics of n and p type Ref. MOSFETs and NCFETs with different  $t_{fe}$  at  $V_{\rm DS}{=}V_{\rm DD}{=}1V$  at iso- $I_{\rm OFF}$ .

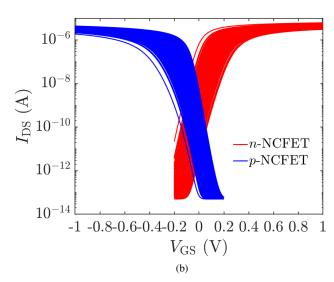

of threshold voltage and the corresponding BSIM4 compact model parameter. We have applied a Gaussian distribution of the threshold voltage parameter with standard deviation obtained from the statistical simulations of the reference MOSFET. We ran Monte Carlo simulations with a statistical ensemble of 1000 devices in the circuit simulator. Fig. 5 shows the ensemble of the transfer characteristics of the two devices with the NCFET clearly displaying lesser variability than the reference bulk device. Note that in this preliminary study, the variability contribution of the ferroelectric layer has not been considered.

### III. STATISTICAL SRAM SIMULATIONS

# A. Setup Details

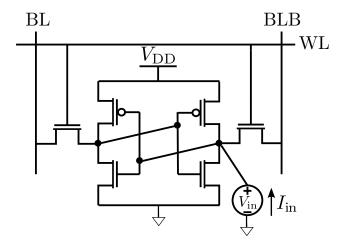

In this section we compare the  $V_{\rm min}$  of the 6-T SRAM cells designed using NCFETs and the conventional reference bulk MOSFETs. In the SRAM cell, the Pull-Up, Pass-Gate and Pull-Down transistor widths are in a ratio of 1:2:3. We have considered the evaluation of the read stability and write ability in terms of the critical currents under read and write conditions ( $I_{\rm crit}$  and  $I_{\rm critw}$  respectively) obtained from the analysis of the respective n-curves [15]. The schematic of the 6T-SRAM cell along with the arrangement for the n-curve measurements is shown in Fig. 6. A DC voltage  $V_{\rm in}$  is applied to the storage node and the current entering the node is recorded, The  $I_{\rm in}-V_{\rm in}$  plots under the READ and WRITE conditions are the n-curves.

Fig. 5. Statistical ensemble of 1000  $I_{\rm DS}-V_{\rm GS}$  characteristics of n and p type (a) Ref. MOSFETs, and (b) NCFETs with  $t_{fe}=$  2nm obtained from Monte-Carlo SPICE simulations.  $V_{\rm DS}$ =0.05V.

It has been previously shown that for the nominal case, the NC-SRAM offers higher  $I_{\rm crit}$  under READ condition as well as higher  $I_{\rm critw}$  under WRITE condition [7]. To examine the impact of variability, we perform 5000 statistical Monte Carlo simulations for the 6T SRAM cells, with the threshold voltage parameter for each nominal transistor having a Gaussian distribution as described in section II-B. The NC-SRAM displays lower relative standard deviation  $(\sigma/\mu)$  for the critical currents.

# B. V<sub>min</sub> Analysis

$V_{\rm min}$  is the minimum supply voltage needed for reliable operation of the SRAM cell. The methodology for  $V_{\rm min}$  calculation is as follows: i) We calculate  $N_{\sigma,Fail}=\mu/\sigma$  as  $V_{\rm DD}$  is varied. Here  $\mu$  and  $\sigma$  are the mean value and standard deviation of the critical currents obtained from 5000 Monte-Carlo runs in the circuit simulator. ii) A target  $N_{\sigma,Fail}$  is set. iii) The  $V_{\rm DD}$  corresponding to the target  $N_{\sigma,Fail}$  is the

Fig. 6. Schematic of the 6-T SRAM cell including the arrangement for the *n*-curve measurements.

$V_{\min}$ . In this work, target  $N_{\sigma,Fail}$  has been set to 5.4.  $V_{\min}$  is known to be limited by variability, and hence NC-SRAMs due to the suppressed variability are expected to achieve lower  $V_{\min}$  relative to the regular SRAMs. Indeed, we find that the NC-SRAMs offer better  $V_{\min}$  than their regular counterparts. Fig. 7 shows the percentage improvement in  $V_{\min}$  when considering the critical current variability obtained from the READ n-curve ( $I_{\text{crit}}$ ). It can be seen that for the  $V_{\min}$  derived from  $I_{\text{crit}}$ , the advantage of NCFETs initially increases with  $t_{fe}$  till an optimum value ( $t_{fe}$ = 2 nm corresponds to a 34% reduction in  $V_{\min}$ ) and then starts to decrease at higher  $t_{fe}$ .

However, for the  $V_{\rm min}$  derived from  $I_{\rm critw}$ , the gains are much lower, with  $t_{fe}{=}$  2 nm showing lesser improvement than  $t_{fe}{=}$  1 nm, while  $t_{fe}{=}$  3 nm cannot fulfill the set criterion. Thus the overall  $V_{\rm min}$  cannot be lowered as much as the  $I_{\rm crit}$  analysis suggests, and the limit to maximum  $t_{fe}$  is set by the WRITE operation. These trends are similar to the reduction of critical current improvement in the nominal SRAMs on increasing the ferroelectric thickness beyond a certain value [7]. It should be noted that for a more comprehensive study, the variability in the ferroelectric layer thickness and properties (the Landau parameters in our modeling approach) should also be taken into account. It is expected that considering this will further diminish the  $V_{\rm min}$  improvement.

# IV. CONCLUSION

Statistical device simulations considering the effects of random discrete dopants, line edge roughness, and metal gate granularity are performed for reference bulk devices. A self-consistent coupling of the standard BSIM4 compact model with the Landau-Khalatnikov equations has been used for compact modeling of the ferroelectric NCFETs. Using statistical circuit simulations utilizing the threshold voltage variability data of reference MOSFETs, we have shown that the better characteristics and immunity of the NCFETs against the baseline MOSFET's conventional statistical variability translates into lower  $V_{\rm min}$  for NCFET based SRAMs, especially under READ condition. This shows that more aggressive  $V_{\rm DD}$  scaling relative to existing CMOS technologies is possible

Fig. 7. Comparison of  $V_{\min}$  for reference SRAM and NC-SRAM with varying  $t_{fe}$  derived from (a) read n-curve ( $I_{\text{critw}}$ ) and (b) write n-curve ( $I_{\text{critw}}$ ).

using NCFETs. As a further work, the impact of the ferroeletric layer itself should also be included in the analysis in order to determine more realistic performance.

## REFERENCES

- [1] S. K. Gupta and K. Roy, "Device-circuit co-optimization for robust design of FinFET-based SRAMs," *IEEE Design & Test*, vol. 30, no. 6, pp. 29–39, 2013.

- [2] X. Zhang, D. Connelly, H. Takeuchi, M. Hytha, R. J. Mears, and T.-J. K. Liu, "Comparison of SOI versus bulk FinFET technologies for 6T-SRAM voltage scaling at the 7-/8-nm node," *IEEE Transactions on Electron Devices*, vol. 64, no. 1, pp. 329–332, 2017.

- [3] S. Salahuddin and S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," *Nano Letters*, vol. 8, no. 2, pp. 405–410, 2008.

- [4] M. Lee, S.-T. Fan, C.-H. Tang, P.-G. Chen, Y.-C. Chou, H.-H. Chen, J.-Y. Kuo, M.-J. Xie, S.-N. Liu, M.-H. Liao et al., "Physical thickness 1.x nm ferroelectric HfZrOx negative capacitance FETs," in *IEEE International Electron Devices Meeting (IEDM)*, 2016, pp. 12.1.1–12.1.4.

- [5] Z. Krivokapic, U. Rana, R. Galatage, A. Razavieh, A. Aziz, J.Liu, J.Shi, H. Kim, R. Sporer, C. Serrao, A.Busquet, P. Polakowski, J. Müller, W. Kleemeier, A. Jacob, D. Brown, A. Knorr, R. Carter, , and S. Banna, "14nm ferroelectric FinFET technology with steep subthreshold slope for ultra low power applications," in *IEEE International Electron Devices Meeting (IEDM)*, 2017.

- [6] M. A. Alam, M. Si, and P. D. Ye, "A critical review of recent progress on negative capacitance field-effect transistors," *Applied Physics Letters*, vol. 114, no. 9, p. 090401, 2019. [Online] https://doi.org/10.1063/1.5092684

- [7] T. Dutta, G. Pahwa, A. R. Trivedi, S. Sinha, A. Agarwal, and Y. S. Chauhan, "Performance evaluation of 7-nm node negative capacitance FinFET-based SRAM," *IEEE Electron Device Letters*, vol. 38, no. 8, pp. 1161–1164, Aug 2017.

- [8] T. Dutta, G. Pahwa, A. Agarwal, and Y. S. Chauhan, "Impact of process variations on negative capacitance FinFET devices and circuits," *IEEE Electron Device Letters*, vol. 39, no. 1, pp. 147–150, Jan 2018.

- [9] T. Dutta, V. P. Georgiev, and A. Asenov, "Random discrete dopant induced variability in negative capacitance transistors," in *Joint Inter*national EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), March 2018.

- [10] T. Dutta, V. P. Georgiev, and A. Asenov, "Interplay of RDF and gate LER induced statistical variability in negative capacitance FETs," in International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Sep., pp. 262–265.

- [11] "GARAND Statistical 3D TCAD Simulator," Synopsys, Inc. Mountain view, CA, USA.

- [12] "BSIM4 compact model, version-4.8 [Verilog-A code]."

- [13] G. Pahwa, T. Dutta, A. Agarwal, S. Khandelwal, S. Salahuddin, C. Hu, and Y. S. Chauhan, "Analysis and compact modeling of negative capacitance transistor with high ON-current and negative output differential resistance Part I: Model description," *IEEE Transactions on Electron Devices*, vol. 63, no. 12, pp. 4981–4985, December 2016.

- [14] S. Mueller, J. Mueller, A. Singh, S. Riedel, J. Sundqvist, U. Schroeder, and T. Mikolajick, "Incipient ferroelectricity in Al-doped HfO<sub>2</sub> thin films," *Advanced Functional Materials*, vol. 22, no. 11, pp. 2412–2417, 2012.

- [15] E. Grossar, M. Stucchi, K. Maex, and W. Dehaene, "Read stability and write-ability analysis of SRAM cells for nanometer technologies," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 11, pp. 2577–2588, Nov 2006.