Wang, L., Brown, A. R., Nedjalkov, M., Alexander, C., Cheng, B., Millar, C., and Asenov, A. (2015) Impact of self-heating on the statistical variability in bulk and SOI FinFETs. *IEEE Transactions on Electron Devices*, 62(7), pp. 2106-2112.

Copyright © 2015 IEEE

A copy can be downloaded for personal non-commercial research or study, without prior permission or charge

Content must not be changed in any way or reproduced in any format or medium without the formal permission of the copyright holder(s)

When referring to this work, full bibliographic details must be given

http://eprints.gla.ac.uk/106385/

Deposited on: 19 June 2015

Enlighten – Research publications by members of the University of Glasgow http://eprints.gla.ac.uk

# Impact of Self-Heating on the Statistical Variability in Bulk and SOI FinFETs

L. Wang, A. R. Brown, *Member, IEEE*, M. Nedjalkov, C. Alexander, B. Cheng, *Member, IEEE*, C. Millar, *Member, IEEE*, and A. Asenov, *Fellow, IEEE*

Abstract—In this paper for the first time we study the impact of self-heating on the statistical variability of bulk and SOI FinFETs designed to meet the requirements of the 14/16nm technology node. The simulations are performed using the GSS 'atomistic' simulator GARAND using an enhanced electro-thermal model that takes into account the impact of the fin geometry on the thermal conductivity. In the simulations we have compared the statistical variability obtained from full-scale electro-thermal simulations with the variability at uniform room temperature and at the maximum or average temperatures obtained in the electro-thermal simulations. The combined effects of line edge roughness and metal gate granularity are taken into account. The distributions and the correlations between key figures of merit including the threshold voltage, on-current, subthreshold slope and leakage current are presented and analysed.

*Index Terms*—CMOS, electro-thermal simulations, FinFETs, statistical variability, correlations

# I. INTRODUCTION

**F** inFETs enable technology scaling at the 22nm CMOS technology generation and beyond because of their excellent electrostatic integrity and control of short channel effects [1]. This is complemented by lower statistical variability due to a tolerance of lower channel doping compared to bulk transistors. Self-heating has been highlighted as one of the areas of concern for FinFETs because of the 3D geometry, the impact of the corresponding 3D heat flow through the fin to the substrate and the impact of the fin geometry on the local thermal conductivity [2-8]. These perceived self-heating problems could be exacerbated in

This Manuscript received December 10, 2014; revised April 21, 2015. The research leading to these results has received funding in part from the European Union Seventh Framework Programme (FP7/2007 – 2013) under grant agreement no. 318458 SUPERTHEME.

L. Wang is with the School of Engineering, University of Glasgow, Glasgow, G12 8LT, UK (e-mail: Liping.Wang@ Glasgow.ac.uk).

A. R. Brown, C. Alexander, B. Cheng and C. Millar are with Gold Standard Simulations Ltd., Glasgow, G12 8LT, UK. (e-mail: a.brown@gold standardsimulations.com; c.alexander@goldstandardsimulations.com; b.cheng @goldstandardsimulations.com)

M. Nedjalkov is with Institute for Microelectronics, TU Wien, Gußhausstraße 2729/E360, 1040 Wien, Austria. (e-mail: Nedialkov@iue.tuwien.ac.at)

A. Asenov is with Gold Standard Simulations Ltd., Glasgow, G12 8LT, and also with Gold Standard Simulations Ltd., Glasgow, G12 8LT, UK. (e-mail: asen.asenov@glasgow.ac.uk).

SOI FinFETs where the thermal conduction towards the substrate is impeded by the low thermal conductivity of the SOI layer beneath the fin [7]. Therefore analyzing and modeling the self-heating in FinFETs and the influence on device performance has become one of the topics attracting a lot of recent interest [2-8].

At the same time, statistical variability introduced by the discreteness of charge and matter has become critically important in contemporary and future CMOS technologies [9-10]. In particular the impact of random discrete dopants (RDDs), fin line edge roughness (FER), gate line edge roughness (GER), and metal gate granularity (MGG) on the variability in bulk and SOI FinFETs have been studied in detail previously [11]. However to the best of our knowledge the impact of self-heating has not be taken into account before in such simulation studies.

In this paper we use the enhanced self-heating simulation capabilities, recently introduced in the GSS 'atomistic' device simulator GARAND [8,12], complemented by the unique capabilities for physical simulation of different sources of statistical variability [13-14], to study, for the first time, the impact of self heating on FinFET variability. The test-bed transistors in this study are bulk and SOI FinFETs designed to meet the specifications for the 14/16nm CMOS technology generation [11].

The paper is organized as follows: In section II we briefly describe the bulk and the SOI FinFETs used as demonstrators in this study. Section III presents the simulation technology including the enhanced electro-thermal simulation method in more detail along with the physical statistical simulation capabilities. The results and analysis of statistical variability in the presence of self-heating effects are presented in Section IV. Finally the conclusions are drawn in Section V.

#### II. THE TESTBED TRANSISTORS

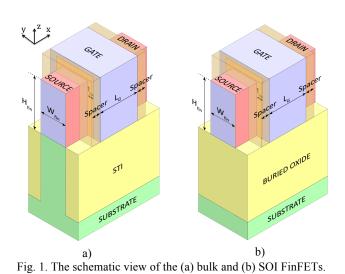

Two n-channel FinFETs, which are on SOI and bulk substrates respectively but have identical dimensions, are used as a test bed in our investigation. Their schematic structures are illustrated in Fig. 1. The nominal device parameters are listed in Table 1. For the bulk FinFET, a  $5 \times 10^{18}$  cm<sup>-3</sup> channel stop doping is introduced below the channel. A conservative channel length of  $L_G$ =25nm was assumed. A high-k gate dielectric is used to minimise gate leakage. Table 2 compares the key figures of merit of the two transistors, which are very similar in terms of performance.

NOMINAL DEVICE PARAMETERS

TABLE I.

| Parameter                        | Value                              |

|----------------------------------|------------------------------------|

| $L_G$                            | 25 nm                              |

| Fin Width, $W_F$                 | 12 nm                              |

| Fin Height, $H_F$                | 30 nm                              |

| Spacer                           | 6 nm                               |

| Extension                        | No extension doping                |

| highly doped drain (HDD) profile | $2nm/dec (\sigma=2.1nm)$           |

| highly doped drain (HDD) doping  | $1 \times 10^{20} \text{ cm}^{-3}$ |

| Equivalent Oxide Thickness (EOT) | 0.8 nm                             |

| Channel stop doping              | $5 \times 10^{18} \text{ cm}^{-3}$ |

| Channel doping                   | $1 \times 10^{15} \text{ cm}^{-3}$ |

| BOX / STI depth                  | 30 nm                              |

| Supply Voltage                   | 0.9 V                              |

TABLE II. THE KEY FIGURES OF MERIT OF THE TWO TRANSISTORS

|                | Bulk FinFET | SOI FinFET |

|----------------|-------------|------------|

| VTlin (Volts)  | 0.286       | 0.294      |

| VTsat (Volts)  | 0.254       | 0.258      |

| SS (mV/decade) | 69.8        | 71.1       |

| DIBL (mV)      | 31.6        | 36.8       |

| IDlin (mA/µm)  | 0.342       | 0.360      |

| IDsat (mA/µm)  | 1.177       | 1.244      |

# III. SIMULATION METHODOLOGY

## A. Electro-thermal simulations

Within the framework of the GSS statistical-variability-aware device simulator GARAND [12], we have developed a thermal simulation module to investigate the impact of self-heating on FinFET DC operation and on the corresponding statistical variability. This module is based on the solution of the coupled Heat Flow, Poisson, and Current Continuity Equations [8].

Usually the electrical characteristics of the device are calculated in a restricted device simulation domain in order to maximize computational efficiency. However, heat is dissipated in a much larger domain, including the active region of the transistor, its neighbors, the substrate, the interconnect layers, the case, and eventually the heat sink. Therefore, realistic thermal boundary conditions rely on thermal resistances, employed to account for heat dissipation into interconnects, the wafer, the case, etc. For given values of thermal resistances, GARAND calculates the temperature differences using an iterative scheme according to the temperature gradient until convergence is achieved.

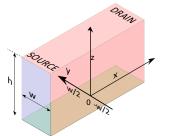

Since the fin thickness (width) is of the order of 10 nm, the thermal conductivity can be significantly reduced compared to bulk Si due to phonon-boundary scattering. We employ a new approximate formula for the calculation of the thermal conductivity in the fin region, which extends the previous 1D formula [15] to 2D [8]. Considering a fin of height h and width w as shown in Fig. 2, the thermal conductivity of the fin is given by

$$\kappa(y, z, T) = \kappa_0(T) \int_0^{\pi/2} \sin^3 \theta \left\{ 1 - \exp\left(-\frac{h}{2\lambda(T)\cos\theta}\right) \cosh\left(\frac{h-2z}{2\lambda(T)\cos\theta}\right) \right\} d\theta$$

$$\int_0^{\pi/2} \sin^3 \theta \left\{ 1 - \exp\left(-\frac{w}{2\lambda(T)\cos\theta}\right) \cosh\left(\frac{-2y}{2\lambda(T)\cos\theta}\right) \right\} d\theta$$

where y and z are the coordinates, T is the lattice temperature,  $\lambda(T)$  is phonon mean free path with temperature dependence,  $\kappa_0(T)$  is the parameterized bulk thermal conductivity with temperature dependence and  $\theta$  is the integral variable.

Fig. 2. A fin of height *h* and width *w*. The *z*-axis is along the direction of fin height with the bottom and top surfaces of the fin being at z=0 and z=h, and the y-axis is along the direction of fin width with the surfaces of the fin being at y=-w/2 and y=w/2.

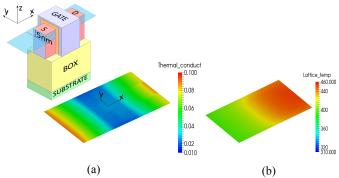

Using this new calculation method, the thermal conductivity of the fin is predicted to be 1~2 orders of magnitude lower than conventional value of the thermal conductivity for bulk Si. In our electro-thermal simulation module, the thermal conductivity at each mesh point in the fin is refreshed according to its spatial position and temperature at each iteration cycle, which ensures the self-consistency of the simulation. By using this formula, the thermal conductivity and lattice temperature in a slice of the fin, which is 5nm below the top gate in the SOI FinFET example, resulting from the self-consistent simulations are illustrated in Fig. 3. The thermal conductivity in the middle of the fin is 0.027W/(cm K). Currently the parameters are adopted from [15], which can be recalibrated if novel experimental data for a nanoscale fin structure becomes available in literature. The anisotropy of thermal conductivity is not included in this work, but will be considered at a future stage.

In the electro-thermal simulations of the bulk and SOI FinFETs, at the bottom of the simulation domain and at the top of the source and drain contacts external thermal resistances are employed and the temperature at these boundaries is calculated according to the values of thermal resistances and heat flow. 2×10<sup>6</sup> K/W substrate thermal resistance and two 1×10<sup>6</sup> K/W contact thermal resistances have been used in this case based on rough estimation. The external thermal resistances are user-specified parameters for the electro-thermal simulation module. The values used here are just for demonstration. A good estimation for external thermal resistances should consider the bulk resistance, interface resistances, effects of heat radiation and spreading. The Masetti model [16] is used for doping-dependent low-field mobility, enhanced Lombardi model [17] is used for perpendicular field-dependent mobility and Caughey-Thomas model [18] is used for lateral field-dependent mobility. Temperature dependency is included in the mobility models and saturation velocity. The reduced thermal conductivity of the fin is taken into account according to Eq. (1).

Fig. 3. (a) Thermal conductivity and (b) lattice temperature in a slice of the fin which is 5nm below the top gate in the SOI FinFET example, at Vg=Vd=0.9V, finally obtained from the self-consistent simulation. Inset: schematic showing the cut plane.

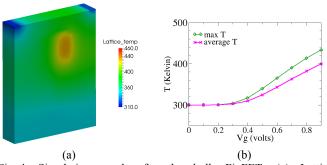

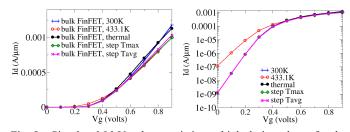

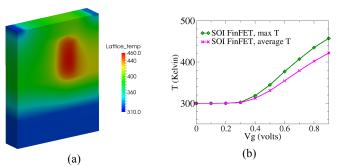

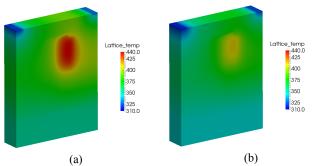

simulated The corresponding lattice temperature distribution at high drain voltage (0.9V) and gate bias of 0.9V for the bulk FinFET is illustrated in Fig. 4 (a). At different gate bias, the maximum lattice temperature and average temperature of the fin resulting from the electro-thermal simulations are illustrated in Fig. 4 (b), which show how device temperature is evolving as a function of Vg. The corresponding Id-Vg characteristics are shown in Fig. 5, where the plotted Id is the total drain current divided by the effective fin width, i.e.  $W = 2H_F + W_F$ . The corresponding simulation results for the SOI FinFET are illustrated in Fig. 6 and Fig. 7. Due to the much lower thermal conductivity of the fin, a significant hot spot is produced near the drain, with peak lattice temperature reaching 457K in the SOI FinFET and reaching 433K in the bulk FinFET. This also indicates strong temperature gradients in the region, which affect the local current density through the additional part related to thermal gradient  $\nabla T_L$ :

$$J_n = qn\mu_n E_n + k\mu_n T_L \nabla n + k\mu_n n \nabla T_L$$

(2)

where *n* is the electron density,  $\mu_n$  is the electron mobility, *k* is Boltzmann constant.

For comparison, simulations without self-heating, where the lattice temperature is geometrically uniform in the device region, are performed. Results are presented at uniform room temperature and at the temperature corresponding to the maximum temperature observed within the device during the electro-thermal simulations. In addition, we run simulations without self-heating at a constant temperature defined by the maximum temperature (as green lines in Fig. 4(b) and Fig. 6(b)), and defined by the average temperature in the fin (as purple lines in Fig. 4(b) and Fig. 6(b)), at each individual Vd and Vg bias condition obtained from the electro-thermal simulations, which is denoted as "step Tmax" and "step Tavg" respectively. As shown in Fig. 5 and Fig. 7, the self-heating produces higher drain current in the Vg range of 0.4~0.7V, the reason being that the impact on the Vth/SS is stronger than the mobility reduction.

Fig. 4. Simulation results for the bulk FinFET. (a) Lattice temperature profile in the middle at Vg=Vd=0.9V; (b) maximum temperature and average temperature in the fin at high drain voltage

Fig. 5. Simulated Id-Vg characteristics at high drain voltage for the bulk FinFET. Left: on linear scale; right: on logarithmic scale. The self-heating produces lower on-current, however, its impact is different from uniform temperature simulations.

Fig. 6. Simulation results for the SOI FinFET. (a) Lattice temperature profile in the middle at Vg=Vd=0.9V; (b) maximum temperature and average temperature in the fin at high drain voltage.

Fig. 7. Simulated Id-Vg characteristics at high drain voltage for the SOI FinFET. Left: on linear scale; right: on logarithmic scale. The self-heating produces lower on-current, however, its impact is different from uniform temperature simulations.

#### B. Statistical variability simulations

The electro-thermal simulation module is integrated seamlessly with the statistical variability simulation capability of GARAND. Line edge roughness (LER) is modelled with the assumption that it follows a Gaussian autocorrelation function [19]. Both gate edge roughness (GER) and fin edge roughness (FER) are included in the simulations, with three times root-mean-square deviation of the gate edge position of  $3\Delta = 2$  nm and a correlation length of  $\Lambda = 30$  nm. In the modelling of MGG we assume a TiN metal gate with an average grain diameter of 5 nm and two major grain orientations which lead to a work-function (WF) difference of 0.2 V, and the probability for the lower and higher WF are 0.4 and 0.6 respectively [20-23]. For both bulk and SOI FinFET examples, ensembles of 400 microscopically different devices were simulated using the automated GSS cluster simulation technology, including combined sources of variability GER, FER and MGG.

The standard deviations of the threshold voltage are very similar for the two FinFETs: 19mv and 21mV for the bulk and the SOI FinFETs respectively. Correspondingly, the matching factors (defined as  $A_{VT} = \sigma_{\Delta VT} \sqrt{WL} = \sqrt{2}\sigma_{VT} \sqrt{WL}$ ) for the two FinFETs are 1.14 mV.µm and 1.25 mV.µm respectively, where *W* in this case is the effective fin width,  $W = 2H_F + W_F$ .

### IV. ELECTRO-THERMAL STATISTICAL VARIABILITY STUDY

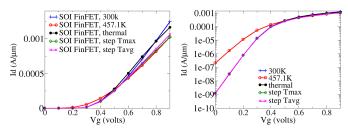

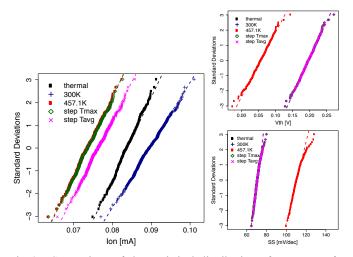

Electro-thermal simulations have been performed on the FinFETs with statistical variations as detailed in Section III (B), and corresponding figures of merit including on-current  $(I_{on})$ , threshold voltage  $(V_{th})$ , the subthreshold slope (SS) and the off-current  $(I_{off})$  have been extracted. Fig. 8 shows the statistical distribution of the figures of merit at drain bias of 0.9V for the bulk FinFET obtained from the electro-thermal simulations, and the analogous distributions for the SOI FinFET are shown in Fig. 9. For comparison, results from variability simulations without self-heating for different cases as specified in Section III (A) are also plotted in these two figures. In these comparison simulations, the lattice temperature is geometrically uniform in the device region, and the value from the characteristics of the nominal device is used as the nominal temperature. Here Vth is VTsat and SS is extracted from the saturation curve.

Fig. 8. Comparison of the statistical distribution of on-current for the bulk FinFET obtained from the electro-thermal simulations with uniform temperature simulation results without self-heating. Insets: threshold voltage and subthreshold slope. All at high drain bias. Impact of self-heating on the statistical distribution of the on-current is clearly shown, especially the reduction of the  $I_{on}$  variability.

It is not surprising that the self-heating only affects the distribution of the on-current (I<sub>on</sub>) in the case of DC operation. The rest of the figures of merit are related to the subthreshold region where the self-heating effects are minimal, therefore there is no observable difference between the uniform room temperature simulation and the electro-thermal simulations. What is somewhat surprising is that the self-heating significantly reduces the Ion variability according to the electro-thermal simulations. The effect is more pronounced in the SOI FinFET where the self-heating is stronger. The explanation of this effect is related to a negative feedback associated with the statistical distribution of Ion. Devices from the higher-current part of the statistical distribution suffer more from the self-heating and their current is more reduced compared to the devices from the lower end of the statistical distribution. In order to illustrate this point Fig. 10 compares the temperature distribution of the two bulk FinFETs from Fig. 8 with the highest and lowest currents in the distribution. The maximum temperature in the first case is 440.8K and the maximum temperature in the second case is 410.8K, because microscopically the structures of the two cases are different due to different GER, LER and MGG patterns, leading to field and current density differences, and the corresponding differences in the heat generation.

Fig. 9. Comparison of the statistical distribution of on-current for the SOI FinFET obtained from the electro-thermal simulations with uniform temperature simulation results without self-heating. Insets: threshold voltage and subthreshold slope. All at high drain bias. Impact of self-heating on the statistical distribution of the on-current is clearly shown, especially the reduction of the  $I_{on}$  variability.

Fig. 10. Temperature distribution of the two bulk FinFETs from Fig. 8(a) with the (a) highest and (b) lowest currents in the distribution.

The averages and the standard deviations of Ion in the five types of simulations presented in Fig. 8 and Fig. 9 are summarized in Table 3. It verifies that both the average  $(\mu)$ and the standard deviation ( $\sigma$ ) for I<sub>on</sub> have been reduced because of the self-heating effects. Due to the thermal isolation of the buried oxide, these effects are stronger in the SOI FinFET, where standard deviation of Ion reduced 1.1 µA from 3.7µA at uniform room temperature according to results from electro-thermal simulations. For bulk FinFET, the standard deviation of  $I_{on}$  reduced 0.7  $\mu A$  from 3.4 $\mu A$  at uniform room temperature according to results from electro-thermal simulations. Looking at the normalized standard deviation of Ion, electro-thermal simulations give the results of 3% for both bulk and SOI FinFETs. Contrarily, a uniform increase in the temperature has a different impact: the reduction of average Ion is larger, while the standard deviation is comparable, therefore statistical variability is enlarged from the viewpoint of the normalized standard deviation (approximately 4% both for the bulk and the SOI FinFET examples). This means uniform increase of temperature in the whole device region cannot accurately reflect the trends of Ion variation, and the temperature gradient in the channel needs to be included when considering the full picture of self-heating effects.

TABLE III. THE MEAN AND STANDARD DEVIATION OF ON-CURRENT, EXTRACTED FROM SIMULATIONS FOR A STATISTICAL ENSEMBLE OF 400.

| I <sub>on</sub><br>(mA)                                                  |                     | Bulk<br>FinFET | SOI<br>FinFET |

|--------------------------------------------------------------------------|---------------------|----------------|---------------|

| Uniform 300K                                                             | μ                   | 0.0847         | 0.0896        |

|                                                                          | σ                   | 0.0034         | 0.0037        |

|                                                                          | σ <sub>normal</sub> | 4.0%           | 4.1%          |

| Electro-thermal<br>simulations                                           | μ                   | 0.0813         | 0.0838        |

|                                                                          | σ                   | 0.0027         | 0.0026        |

|                                                                          | σ <sub>normal</sub> | 3.3%           | 3.1%          |

| Uniform peak<br>temperature                                              | μ                   | 0.0719         | 0.0736        |

|                                                                          | σ                   | 0.0028         | 0.0029        |

|                                                                          | σ <sub>normal</sub> | 3.9%           | 3.9%          |

| Step Tmax (maximum<br>temperature at each<br>individual step)            | μ                   | 0.0719         | 0.0736        |

|                                                                          | σ                   | 0.0028         | 0.0029        |

|                                                                          | σ <sub>normal</sub> | 3.9%           | 3.9%          |

| Step Tavg (average<br>temperature in the fin at<br>each individual step) | μ                   | 0.0744         | 0.0764        |

|                                                                          | σ                   | 0.0029         | 0.0030        |

|                                                                          | σ <sub>normal</sub> | 3.9%           | 3.9%          |

$\mu$ : mean;  $\sigma$ : standard deviation;  $\sigma_{normal}$ : normalized standard deviation.

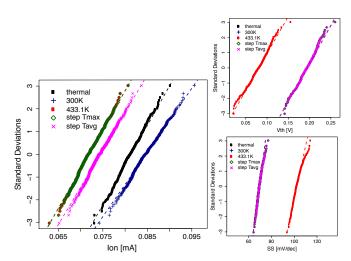

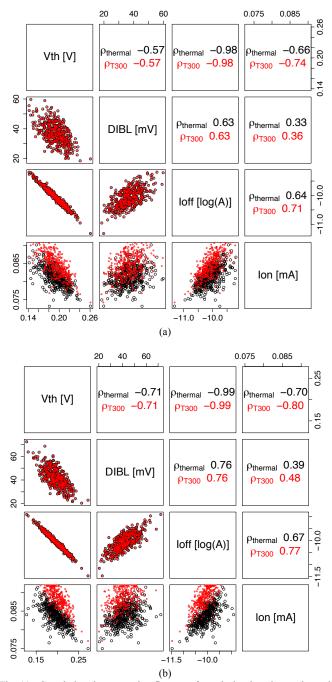

As could be expected, the self-heating strongly affects the correlation between  $I_{on}$  and all other figures of merit. This is illustrated in Fig. 11 for both FinFETs, where the correlation coefficients can be read diagonally. For example, for the bulk FinFET the correlation coefficient between  $I_{on}$  and  $V_{th}$  changes from -0.66 at uniform room temperature to -0.74 according to the electro-thermal simulation, while for the SOI FinFET, change of this correlation coefficient due to self-heating is larger (from -0.70 to -0.80). These will provide useful information for compact modeling.

## V. CONCLUSIONS

In this paper we present results obtained from the electro-thermal simulation of statistical variability in bulk and SOI FinFETs. The electro-thermal simulations take into account the impact of the fin geometry on the thermal conductivity. The reduced thermal conductivity has a dramatic effect on the self-heating, raising the peak temperature to 433K in the case of bulk FinFETs and to 457K in the case of SOI FinFETs. The self-heating has a strong impact in reducing the on-current variability but does not significantly affect the threshold voltage, subthreshold slope and off current variability. This in turn affects the correlation between the on-current distribution and the distributions of the rest of the figures of merit. This work focuses on the DC operation, while the impact on variability in circuit switching will strongly depend on the workload. A negative feedback between the current variability and the self-heating is indicated from our simulation.

In contrast, uniform increase of temperature in the whole device region cannot accurately reflect the trends of  $I_{on}$  variation, and the temperature gradient in the channel needs to be included when considering the full picture of self-heating effects.

Fig 11. Correlation between the figures of merit in the electro-thermal statistical simulation (in black) of (a) bulk and (b) SOI FinFETs, comparing to results with uniform lattice temperature at 300K (in red). The correlation coefficients can be read diagonally. The self-heating strongly affects the correlation between  $I_{on}$  and all other figures of merit.

#### REFERENCES

[1] C. Auth, C. Allen, A. Blattner, D. Bergstrom, M. Brazier, M. Bost, M. Buehler, V. Chikarmane, T. Ghani, T. Glassman, R. Grover, W. Han, D. Hanken, M. Hattendorf, P. Hentges, R. Heussner, J. Hicks, D. Ingerly, P. Jain, S. Jaloviar, R. James, D. Jones, J. Jopling, S. Joshi, C. Kenyon, H.

Liu, R. McFadden, B. Mcintyre, J. Neirynck, C. Parker, L. Pipes, I. Post, S. Pradhan, M. Prince, S. Ramey, T. Reynolds, J. Roesler, J. Sandford, J. Seiple, P. Smith, C. Thomas, D. Towner, T. Troeger, C. Weber, P. Yashar, K. Zawadzki, and K. Mistry, "A 22 nm high per-formance and low-power CMOS technology featuring fully-depleted tri- gate transistors, self-aligned contacts and high density MIM capacitors," in *Proc. VLSI Technol. Symp.*, Jun. 2012, pp. 131–132.

- [2] S. Kumar, R. V. Joshi, C-T. Chuang, K. Kim, J.Y. Murthy, K. T. Schonenbergb, E. J. Nowakc. "Self-consistent and efficient electro-thermal analysis for poly/metal gate FinFETs". IEDM 2006.

- [3] S. Kolluri, K. Endo, E. Suzuki, K. Banerjee. "Modelling and analysis of self-heating in FinFET devices for improved circuit and EOS/ESD performance". IEDM 2007.

- [4] Chuan Xu, S. Kolluri, K. Endo, E. Suzuki, K. Banerjee. "Analytical thermal model for self-heating in advanced FinFET devices with implications for design and reliability." IEEE Transactions on Computer-aided Design of Integrated Circuits and Systems. Vol 32, No.7, pp.1045-1058.

- [5] M. Shrivastava, M. Agrawal, S. Mahajan, H. Gossner, T. Schulz, D. K. Sharma, and V. R. Rao. "Physical Insight Toward Heat Transport and an Improved Electrothermal Modeling Framework for finfet Architectures". IEEE Transactions on Electron Devices, VOL. 59, NO. 5, MAY 2012. pp 1353-1363

- [6] M. Braccioli1, G. Curatola, Y. Yang, E. Sangiorgi, C. Fiegna. "Simulation of Self-Heating effects in 30nm gate length FinFET". ULIS 2008. Pp. 71-74.

- [7] A.J. Scholten, G.D.J. Smit, R.M.T. Pijper, L.F. Tiemeijer, H.P. Tuinhout, J.-L.P.J. van der Steen. "Experimental assessment of self-heating in SOI FinFETs". IEDM 2009.

- [8] L. Wang, A. R. Brown, M. Nedjalkov, C. Alexander, B. Cheng, C. Millar, A. Asenov. "3D Coupled Electro-Thermal Simulations for SOI FinFET with Statistical Variations Including the Fin Shape Dependence of the Thermal Conductivity", in *Proceedings of SISPAD*, Sep. 2014. pp. 269-272, 2014.

- [9] J. Mazurier, O. Weber, F. Andrieu, F. Allain, L. Tosti, L. Brevard, O. Rozeau, M.-A. Jaud, P. Perreau, C. Fenouillet-Beranger, F. A. Khaja, B. Colombeau, G. De Cock, G. Ghibaudo, M. Belleville, O. Faynot, and T. Poiroux, "Drain current variability and MOSFET parameters correlations in planar FDSOI technology," in *Proc. IEEE IEDM*, Dec. 2011, pp. 575–578. 2013

- [10] J. Mazurier, O. Weber, F. Andrieu, A. Toffoli, F. Allain, P. Perreau, C. Fenouillet-Beranger, O. Thomas, M. Belleville, and O. Faynot, "On the variability in planar FDSOI technology: From MOSFETs to SRAM cells," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2326–2336, Aug. 2011.

- [11] Andrew R. Brown, Nicolas Daval, Konstantin K. Bourdelle, Bich-Yen Nguyen, and Asen Asenov. "Comparative Simulation Analysis of Process-Induced Variability in Nanoscale SOI and Bulk Trigate FinFETs". IEEE Trans. Electron. Dev., Vol. 60, No. 11, pp. 3611-3617, November 2013.

- [12] GARAND Statistical 3D TCAD Simulator [Online]. Available: http://www.GoldStandardSimulations.com/products/garand/

- [13] X. Wang, B. Cheng, A. R. Brown, C. Millar, and A. Asenov, "Statistical variability in 14-nm node SOI FinFETs and its impact on corresponding 6T-SRAM cell design," in *Proc. ESSDERC*, Sep. 2012, pp. 113–116.

- [14] B. Cheng, A. R. Brown, X. Wang, and A. Asenov, "Statistical variability study of a 10nm gate length SOI FinFET device," in *Proc. Silicon Nanoelectron. Workshop*, Jun. 2012, pp. 1–2.

- [15] D. Vasileska, K. Raleva, S. M. Goodnick, "Electrothermal studies of FD SOI devices that utilize a new theoretical model for the temperature and thickness dependence of the thermal conductivity". IEEE Trans. Electron. Dev., Vol. 57, No. 3, pp.726-728, 2010.

- [16] M. Severi G. Masetti and S. Solmi. Modeling of carrier mobility against carrier concentration in Arsenic-, Phosphorous-, and Boron-doped Silicon. *IEEE Trans. Elec. Dev.*, Vol. 30, pp.764–769, 1983.

- [17] C. Lombardi, S. Manzini, A. Saporito, and M. Vanzi. A physically based mobility model for nu- merical simulation of nonplanar devices. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol.* 7, No. 11, pp. 1164 –1171, Nov 1988.

- [18] D.M. Caughey and R.E. Thomas. Carrier mobilities in silicon empirically related to doping and field. *Proceedings of the IEEE*, *Vol.* 55, No. 12, pp.2192 – 2193, Dec. 1967.

- [19] A. Asenov, S. Kaya, and A. R. Brown, "Intrinsic parameter fluctuations in decananometer MOSFETs introduced by gate line edge roughness," *IEEE Trans. Electron Devices*, vol. 50, no. 5, pp. 1254–1260, May 2003.

- [20] H. Dadgour, K. Endo, V. De, and K. Banerjee, "Modeling and analysis of grain-orientation effects in emerging metal-gate devices and implications for SRAM reliability," in *Proc. IEEE IEDM*, Dec. 2008, pp. 705–708.

- [21] K. Ohmori, T. Matsuki, D. Ishikawa, T. Morooka, T. Aminaka, Y. Sugita, T. Chikyow, K. Shiraishi, Y. Nara, and K. Yamada, "Impact of additional factors in threshold voltage variability of metal/high-k gate stacks and its reduction by controlling crystalline structure and grain size in the metal gates," in *Proc. IEEE IEDM*, Dec. 2008, pp. 1–4.

- [22] A. R. Brown, N. M. Idris, J. R. Watling, and A. Asenov, "Impact of metal gate granularity on threshold voltage variability: A full-scale 3D statistical simulation study," *IEEE Electron Device Lett.*, vol. 31, no. 11, pp. 1199–1201, Nov. 2010.

- [23] X. Wang, A. R. Brown, N. Idris, S. Markov, G. Roy, and A. Asenov, "Statistical threshold-voltage variability in scaled decananometer bulk HKMG MOSFETs: A full-scale 3D simulation scaling study," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2293–2301, Aug. 2011.

Liping Wang received the B.S. degree in Optical and Physical Electronics, and the Ph.D. degree in Electronic Science and Technology, from Xi'an Jiaotong University, Xi'an, China, in 1995 and 2000 respectively. From 2000 to 2002, she worked as a postdoc in Cavendish Laboratory, Cambridge University. She joined the Device Modelling

Group, School of Engineering, University of Glasgow in 2011, after more than 7 years of industrial experience in a specialized CAD software company based in London. She is currently working on TCAD process simulations, electro-thermal simulations, and software integrations and simultaneous simulation of process and statistical variations.

Andrew R. Brown (M'09) received the B.Eng (Hons) degree in Electronics & Electrical Engineering from the University of Glasgow, Glasgow, UK in 1992. He is currently with Gold Standard Simulations, Ltd. working as the Chief Developer for the TCAD device simulator Garand.

**Mihail Nedjalkov** received a master's degree in physics at the Sofia University, Bulgaria, a PhD degree (1990), habilitation (2001) and D.Sc. degree (2011) at the Bulgarian Academy of Sciences (BAS). He is Associate Professor at the Institute of Information and Communication Technologies, BAS, and

visiting scientists at the Institute for Microelectronics, *Technische Universität Wien*. His research interests include physics and modeling of classical and quantum carrier transport in semiconductor materials, devices and nanostructures, collective phenomena, theory and application of stochastic methods.

**Craig Alexander** obtained his M.Sci degree in joint physics and astronomy from the University of Glasgow in 2001 before studying for his Ph.D within Glasgow University's Device Modelling Group. There he developed 3D Monte Carlo simulation tools for assessing statistical variability in

nano-scale transistors and, after a period as a post doctoral research associate, joined Gold Standard Simulations in 2012 where he leads the Monte Carlo simulation development.

**Binjie Cheng** (M'11) received the B.S. degree, M.S. degree in Optical and Physical Electronic Engineering, Ph.D. degree in Electronic Science and Technology from Xi'an Jiaotong University, Xi'an, China, in 1994, 1997 and 2000, respectively. He was a Research Fellow with the School of

Engineering, University of Glasgow. Currently he is with Gold Standard Simulations Ltd, working on TCAD, statistic compact modelling and design technology co-optimization.

**Campbell Millar** (M09) received his BEng degree in Electronics Engineering and Music from the University of Glasgow in 1999, he received his PhD in 2003 from the University of Glasgow. He was a Senior Research Fellow in the School of Engineering at the University of Glasgow before moving to Gold Standard

Simulations Ltd. where he is currently the VP for Software Development.

Asen Asenov (M'96, SM'05, F'11) received a PhD degree in solid state physics from the Bulgarian Academy of Science in 1989. He is currently CEO of Gold Standard Simulations Ltd. and a James Watt Professor of Electrical Engineering at Glasgow University.